**Universidad Internacional de La Rioja**

**Máster universitario en Seguridad Informática**

Implementación basada en

co-simulación HW de un

algoritmo criptográfico en

una FPGA.

**Trabajo Fin de Máster**

**presentado por:** Fernández Herrera, David Guillermo

**Director/a:** Botella, Guillermo

**Ciudad:** Madrid

**Fecha:** 25 de Julio de 2014

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

## Resumen

Debido a la naturaleza de gran multitud de algoritmos criptográficos de realizar tareas computacionalmente intensivas y que posibilitan un alto grado de paralelismo en sus operaciones, la utilización de FPGAs para su implementación puede ser una solución óptima.

El tiempo dedicado a la verificación de los diseños en FPGA es uno de los grandes obstáculos en los proyectos que utilizan estos dispositivos, debido principalmente a la lentitud de las simulaciones realizadas en PC y por la dificultad que implica realizar un banco de pruebas complejo en un lenguaje de descripción hardware. Para solucionar estos problemas, el presente Trabajo Fin de Máster describe cómo desarrollar una sencilla aplicación genérica para gestionar la entrada/salida de datos desde el entorno Simulink y transmitirlos de forma eficiente a un algoritmo que se esté ejecutando en una FPGA mediante co-simulación Hardware. Para tal propósito, se hace uso de la herramienta System Generator de Xilinx.

**Palabras Clave:** Co-Simulación, Criptografía, System Generator, FPGA, Hardware

## Abstract

Due to the nature of a great multitude of cryptographic algorithms to perform computationally intensive tasks and exhibit high degree of parallelism, the use of FPGAs for its implementation can be an optimal solution.

The time dedicated to the verification of FPGA designs is one of the major obstacles in projects utilizing this kind of devices. It is mainly due to the slowness of the simulations running on PC and the difficulty of making complex test benches using hardware description languages. To solve these problems, this work describes how to develop a simple generic application using Simulink for managing input and output data of an algorithm running on FPGA and how to transmit data between FPGA and PC at high speed using Hardware Co-Simulation. System Generator tool is used to achieve these goals.

**Keywords:** co-simulation, cryptography, System Generator, FPGA, Hardware

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

## Contenido

|                                                     |    |

|-----------------------------------------------------|----|

| Resumen.....                                        | 2  |

| Abstract.....                                       | 2  |

| 1. Introducción .....                               | 6  |

| 2. Marco Teórico .....                              | 8  |

| 3. Objetivos .....                                  | 10 |

| 4. Metodología .....                                | 12 |

| 4.1. Elección de la tecnología.....                 | 12 |

| 4.2. Elección de los algoritmos .....               | 17 |

| 4.2.1. Funciones resumen SHA .....                  | 18 |

| 4.3. Implementación algoritmos .....                | 19 |

| 4.3.1. SHA1 .....                                   | 19 |

| 4.3.2. SHA256 .....                                 | 21 |

| 4.3.3. SHA 512 .....                                | 24 |

| 4.4. Elección de la plataforma.....                 | 26 |

| 5. Contribución.....                                | 28 |

| 5.1. Requisitos iniciales .....                     | 29 |

| 5.2. Tecnologías empleadas.....                     | 30 |

| 5.2.1. Herramientas para el desarrollo en PC .....  | 30 |

| 5.2.2. Herramientas para el desarrollo en FPGA..... | 32 |

| 5.2.3. Interfaz de comunicación PC-FPGA.....        | 34 |

| 5.3. Descripción de la aplicación .....             | 34 |

| 5.3.1. Modelos de referencia.....                   | 36 |

| 5.3.2. Algoritmos FPGA .....                        | 37 |

| 5.3.2.1. SHA 256 .....                              | 37 |

| 5.3.2.1.1. Implementación.....                      | 37 |

| 5.3.2.1.2. Verificación .....                       | 42 |

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

|                                                          |    |

|----------------------------------------------------------|----|

| 5.3.2.2. SHA1 .....                                      | 44 |

| 5.3.2.2.1. Implementación.....                           | 44 |

| 5.3.2.2.2. Verificación .....                            | 46 |

| 5.3.2.3. SHA 512.....                                    | 47 |

| 5.3.2.3.1. Implementación.....                           | 47 |

| 5.3.2.3.2. Verificación .....                            | 48 |

| 5.3.3. Framework de intercomunicación.....               | 49 |

| 5.3.3.1. Hito 1 .....                                    | 51 |

| 5.3.3.1.1.1. Implementación .....                        | 51 |

| 5.3.3.1.1.2. Verificación.....                           | 57 |

| 5.3.3.2. Hito 2a.....                                    | 60 |

| 5.3.3.2.1.1. Implementación .....                        | 60 |

| 5.3.3.2.1.2. Verificación.....                           | 63 |

| 5.3.3.3. Hito2b .....                                    | 64 |

| 5.3.3.3.1.1. Implementación .....                        | 64 |

| 5.3.3.3.1.2. Verificación .....                          | 65 |

| 5.3.3.4. Hito 3.....                                     | 66 |

| 5.3.3.4.1.1. Implementación .....                        | 66 |

| 5.3.3.4.1.2. Verificación.....                           | 70 |

| 6. Resultados .....                                      | 73 |

| 6.1. Algoritmos en lenguaje de descripción hardware..... | 73 |

| 6.1.1. Lógica utilizada .....                            | 73 |

| 6.1.2. Frecuencia de Funcionamiento .....                | 75 |

| 6.1.3. Consumo.....                                      | 76 |

| 6.1.4. Tiempos de Simulación.....                        | 78 |

| 6.2. Co-simulación Hardware.....                         | 78 |

| 6.2.1. Lógica utilizada .....                            | 79 |

| 6.2.2. Frecuencia de Funcionamiento .....                | 79 |

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

|                                                                |     |

|----------------------------------------------------------------|-----|

| 6.2.3. Consumo.....                                            | 79  |

| 6.2.4. Tiempos de simulación.....                              | 80  |

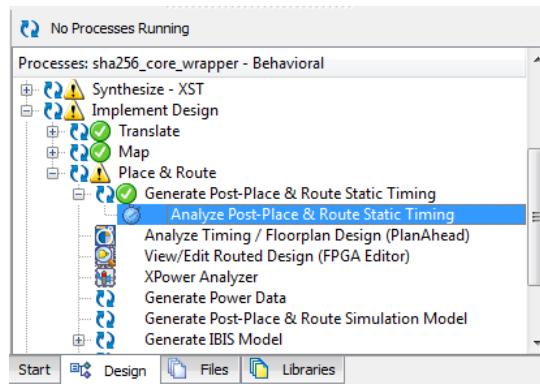

| 6.2.5. Place&Route .....                                       | 81  |

| 7. Conclusiones.....                                           | 82  |

| 8. Proyección de futuro .....                                  | 86  |

| 9. Bibliografía/Referencias .....                              | 87  |

| 10. Anexo I. Código.....                                       | 90  |

| 10.1. Funciones Matlab.....                                    | 90  |

| 10.1.1. “read_input_file.m”.....                               | 90  |

| 10.1.2. “write_output_file.m” .....                            | 93  |

| 10.1.3. “read_input_file_sharedFifos.m” .....                  | 95  |

| 10.1.4. “write_output_file_sharedFifos.m” .....                | 98  |

| 10.1.5. “read_input_file_sharedFifos_h2.m” .....               | 100 |

| 10.1.6. “write_output_file_sharedFifos_h2.m” .....             | 103 |

| 10.1.7. “sha256_core_config.m” .....                           | 106 |

| 10.2. Código VHDL.....                                         | 109 |

| 10.2.1. Ficheros Implementación.....                           | 109 |

| 10.2.1.1. Sha256.vhd .....                                     | 109 |

| 10.2.1.2. sha160_wrapper.vhd .....                             | 118 |

| 10.2.1.3. sha512_wrapper.vhd .....                             | 120 |

| 10.2.2. Ficheros Verificación .....                            | 123 |

| 10.2.2.1. tb_sha_256.vhd .....                                 | 123 |

| 10.2.2.2. Fichero para simulación en ModelSim: sha_256.do..... | 128 |

## 1. Introducción

En la actualidad existen potentes dispositivos para desarrollar tareas computacionalmente intensivas, como pueden ser las propias de algunos algoritmos criptográficos. Dichos dispositivos utilizados como co-procesadores liberarán a los procesadores principales de la carga computacional asociada a dichas tareas.

Se propone la implementación de varios algoritmos criptográficos en una FPGA (Field Programmable Gate Array) al considerarse, tras realizar un análisis de distintas tecnologías disponibles, el dispositivo más adecuado. Existen numerosos artículos académicos sobre implementaciones de este tipo, pero el principal objetivo del presente trabajo no es la implementación en sí del algoritmo en una FPGA, sino la presentación de una arquitectura que facilite la verificación de los diseños realizados, acortando los tiempos de desarrollo de los bancos de pruebas y acelerando la realización de dichas pruebas.

Esta arquitectura se basa en el uso de herramientas de Mathworks y Xilinx trabajando conjuntamente para permitir modelar sistemas destinados a ser ejecutados en FPGA.

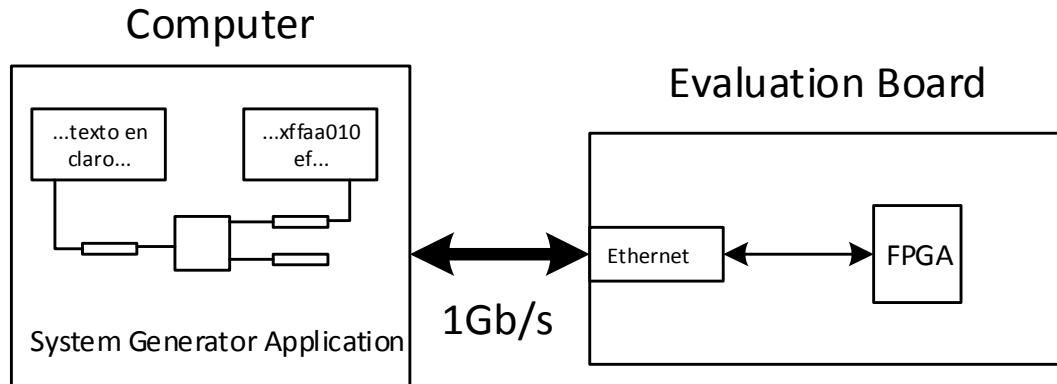

En el presente Trabajo Fin de Máster se desarrollará una aplicación que ejecute en FPGA un algoritmo criptográfico y en la que se intercambien datos entre este dispositivo y el PC eficientemente. Para ello, se empleará una tarjeta de evaluación (ML605 de Xilinx) conectada al PC a través de conexión Gigabit Ethernet permitiendo de esta forma, alcanzar una elevada tasa de transferencia de datos.

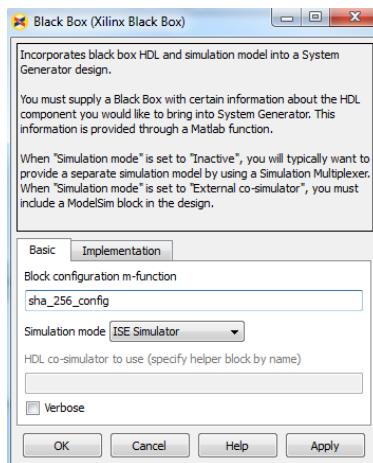

A este proceso, se le denomina co-simulación Hardware. El algoritmo criptográfico se tratará dentro de la aplicación como una caja negra (Black Box), de forma que pueda ser reemplazado por cualquier otro algoritmo sin alterar la estructura del Framework desarrollado.

Se comenzará describiendo el contexto de la aplicación indicando las referencias empleadas o desestimadas junto a las razones que llevaron a tales decisiones. Se definirán unos objetivos concretos y se describirá la metodología seguida en el desarrollo de la aplicación para posibilitar alcanzarlos.

Para comprender el funcionamiento de la aplicación desarrollada resulta de vital importancia realizar una descripción de las herramientas involucradas en su desarrollo, ya que éstas posibilitan la automatización de gran número de las acciones requeridas para la configuración

del dispositivo. Mathworks aporta Matlab y Simulink para simplificar el proceso de generación y análisis de datos. Por otro lado, estas dos herramientas proporcionan una enorme potencia matemática para la gestión de dichos datos. Simulink es un producto que se ejecuta sobre Matlab, que proporciona un entorno de interactivo y gráfico para el modelado, la simulación y análisis de sistemas dinámicos.

System Generator de Xilinx permite al entorno gráfico Simulink utilizar bloques que pueden ser sintetizados directamente en una FPGA facilitando su implementación. Entre una de sus principales funciones destaca el uso de “black boxes”, lo que permite importar componentes desarrollados en lenguajes de descripción hardware a Simulink, de forma que puedan tratarse como cualquier otro bloque dentro del interfaz gráfico.

Los algoritmos criptográficos que se decidan implementar deberán ser adaptados para permitir su integración en la aplicación sin que se requiera modificar la gestión de los datos de entrada/salida. La aplicación será un modelo de Simulink en el que los distintos algoritmos a verificar se tratarán como cajas negras, de manera que para utilizar el mismo modelo para distintos algoritmos baste con intercambiar los bloques que los representan. Antes de generar dichos bloques se realizarán una serie de simulaciones sobre el código fuente para verificar su funcionamiento. De estas pruebas se obtendrán unos tiempos de simulación que permitirán comparar este tipo de verificaciones con la propuesta en este Trabajo.

Para lograr el objetivo principal de este Trabajo se han ido alcanzando una serie de hitos que serán detallados en profundidad en otros apartados. En el primer Hito se desarrollará una sencilla aplicación que se ejecute íntegramente en PC haciendo uso de los componentes tipo “black box”. Su objetivo será la verificación del proceso de generación de los componentes. En el segundo Hito, sobre la aplicación anterior se realizarán una serie de modificaciones que permitan la separación de la ejecución en dos dominios, PC y FPGA. Las modificaciones realizadas se verificarán en PC para simplificar la depuración de los posibles problemas que surjan. En el tercer Hito se realizará la co-simulación HW, ejecutando el algoritmo en una tarjeta de evaluación basada en FPGA y gestionando los datos desde el PC.

Durante la consecución de los distintos hitos se obtendrán los resultados de los que se derivarán las conclusiones finales.

## 2. Marco Teórico

El presente apartado abarca el estudio de la literatura existente, donde se analiza y describe el contexto asociado a la línea de trabajo escogida. Se comentarán las referencias empleadas y las causas por las que se ha decidido emplearlas o descartarlas.

En el planteamiento inicial de este Trabajo se proponía la implementación de varios algoritmos criptográficos en una FPGA usando un lenguaje de descripción hardware. Se comenzó analizando el estado del arte en cuanto a implementaciones de este tipo, y se observó que existían multitud de publicaciones al respecto. Algunas de ellas resultan particularmente muy interesantes como en el trabajo de Song, Kawakami, Nakano e Ito (2010) [1], en el que se plantea una implementación para el algoritmo RSA (2048bits) mediante un único DSP Slice (hardware específico que incorporan las FPGAS destinado a hacer operaciones DSP, compuesto normalmente por varios multiplicadores, sumadores y registros) y un Block Ram (bloque de memoria interna de la FPGA) para la familia de FPGAs Virtex-6 de Xilinx. Kshirsagar y Vyawahe (2012) [2] proponen una implementación con gran rendimiento y una importante reducción de la lógica empleada enfocándose en un dispositivo Spartan3 de Xilinx. En el trabajo de McEvoy, Crowe, Murphy y Marnane (2006) [3] se combinan en la implementación del algoritmo SHA2 dos técnicas de optimización muy populares (pipelining y unrolling) para conseguir una gran tasa de procesamiento de datos, aunque es superada por varios trabajos más recientes como el realizado por Madhavi, Hanumantha Rao, Malyadri y Rama Krishna Prasad (2012) [4], en donde aparecen varias tablas muy interesantes comparando los resultados obtenidos con otros trabajos.

Se podrían seguir enumerando muchos otros documentos que aportan novedosas técnicas buscando aumentar la velocidad de procesado o la reducción de la lógica empleada, pero observando que existe tanta información y trabajos al respecto se descartó esta línea de trabajo, ya que se consideró que no se iba a realizar una gran aportación en este campo.

Por otro lado, se consultaron diversos artículos relacionados con implementaciones de algoritmos criptográficos empleando la herramienta System Generator y se ha observado que existe bastante literatura al respecto, ya que esta herramienta permite realizar diseños y validarlos en FPGA sin necesidad de tener conocimientos en lenguajes de descripción hardware. Por tomar un par de ejemplos, Sánchez, Alvarez y Sully Sánchez (2007) [5] proponen una arquitectura basada en filtros para procesado de la imagen y Alia Arshad,

Kanwal Aslam, Dur-e-Shahwar Kundi y Arshad Aziz (2014) en [6] realizan una implementación del algoritmo criptográfico AES que puede ser ejecutada a 288.19 MHz con una tasa de salida de 36.864 Gbps.

Respecto a la co-simulación hardware no se han encontrado muchos trabajos al respecto. En el trabajo de Panduranga, Kumar y Sharath Kumar (2013) [7] se comenta una aplicación sobre cifrado de imágenes múltiples pero no se describe cómo realizar la co-simulación. Quizás la publicación más relacionada con este Trabajo sea la de Denning, Devlin e Irvine (2004) [8], donde se discute sobre el uso de System Generator para co-simulation hardware en FPGA del algoritmo de cifrado AES-128. En este artículo se muestran datos de cómo se consigue una co-simulación tres veces más rápida usando una red TCP/IP uniendo dos nodos situados a una distancia de aproximadamente 600 kilómetros, que en una simulación convencional de Simulink sobre un PC. Otra co-simulación hardware de este estudio reduce el tiempo de simulación en un 4000% ejecutándose a través del bus PCI. En este artículo, se comenta cómo la co-simulación hardware permite liberar al PC de la carga computacional que conlleva la simulación para poder ser destinado a otras tareas.

Estos trabajos aportan datos sobre las virtudes de usar la co-simulación hardware pero en ninguno de estos trabajos se comenta cómo realizar el proceso que permite llevar a cabo tal co-simulación. Para averiguar cómo implementar esta tarea sin duda alguna la mayor ayuda se ha obtenido del documento de Xilinx “System Generator for DSP User Guide” (2010) [9] y de “System Generator for DSP Reference Guide” (2012) [23] donde se describe el funcionamiento de esta herramienta, así como un video tutorial (Xilinx. Getting Started with System Generator) [10] y la documentación asociada (Xilinx, 2010) [11]. Por otro lado, se ha tenido que consultar en reiteradas ocasiones la ayuda online que proporciona Mathworks para Simulink [12].

El código que se ha utilizado para los algoritmos criptográficos del presente trabajo, se distribuye de forma gratuita bajo licencia GPL (GNU General Public License). Los enlaces de descarga se indican en [13] (Arif Endro, 2010) y [14] (de La Piedra, 2014). La principal referencia a la hora de entender el funcionamiento de dichos algoritmos se ha extraído de [15] (Anónimo) y del trabajo de Dunkelman (2012) [16].

En cuanto a la elección de la tecnología a emplear, existen varios artículos en los que se comparan GPUs, FPGAs y CPUs. En [17], dos investigadores de Microsoft (Sirowy y Forin, 2008) analizan los mecanismos que permiten a las FPGAs sobrepasar a los

microprocesadores en determinadas tareas de cómputo siendo ejecutadas a una frecuencia de reloj mucho menor.

En el estudio de Thomas, Howes y Luk (2009) [18] se realiza una comparativa entre CPUs, GPUs, FPGAs y MPPAs (Massively Parallel Processor Arrays) para un algoritmo de generación de números aleatorios e intenta identificar para cada plataforma la implementación óptima del algoritmo. Resulta interesante este artículo por la breve pero clara definición que realiza de los distintos tipos de dispositivos que analiza y por las tablas de resultados que obtiene. En [19] Cullinan, Wyant y Frattesi (trabajadores de Mathworks) realizan medidas sobre las tres plataformas de cómputo más importantes: CPUs, GPUs y FPGAs; realizando 66 pruebas con el objetivo de que sirvan como referencias para la elección del dispositivo más adecuado para las distintas aplicaciones que se tratan. Es importante destacar que en estas pruebas resulta ganadora en término de operaciones por segundo la GPU, pero debido a que no se incluyen los tiempos en transmisión y recepción de datos. Si se incluyen estos tiempos las FPGAs resultan claras vencedoras. Venugopal y Manikantan Shila (2013) [20] comentan la necesidad de procesado en tiempo real en el cifrado/descifrado de aplicaciones basadas en transmisiones sobre redes y también tratan sobre el grado de paralelismo y las tareas computacionalmente intensivas que caracterizan a los algoritmos criptográficos. Incluye una comparativa de implementaciones de los algoritmos TEA y XTEA en GPU y FPGA. Este artículo propone el uso de una herramienta llamada CHAAT (Cryptographic Hardware Acceleration and Analysis Tool) para facilitar la selección del algoritmo criptográfico óptimo para cada plataforma.

### 3. Objetivos

El principal objetivo de este Trabajo es implementar una arquitectura de comunicación PC-FPGA para la verificación de algoritmos criptográficos y demostrar las mejoras que supone este tipo de arquitectura para acelerar las etapas de diseño y verificación frente a las soluciones que existen basadas únicamente en PC o en FPGA.

Las simulaciones realizadas sobre PC de una aplicación que se ejecutará posteriormente en una FPGA suelen ser muy lentas, y los bancos de pruebas requieren un trabajo muy tedioso para abarcar todas las posibilidades.

Por otro lado, la verificación física sobre FPGA requiere el uso de pines de depuración y un analizador lógico, lo que obliga a que sólo puedan observarse unas pocas señales con cada prueba. Existe la posibilidad de instanciar dentro de la FPGA un analizador lógico que conste de una serie de búferes que almacenen las muestras que se desee observar, para posteriormente visualizarlas a través del JTAG con una herramienta en el PC (ChipScope con la familia de FPGAs de Xilinx). Esta opción presenta la limitación de que el analizador lógico usará recursos de la propia FPGA y puede incluso llegar a afectar al funcionamiento del sistema, puesto que al instanciar este componente, el diseño podría incumplir los requerimientos de frecuencia máxima impuestos.

La generación de vectores de entrada y análisis de los datos de salida haciendo uso del lenguaje de programación Matlab y del interfaz gráfico Simulink, añadirá unas ventajas importantes en cuanto a potencia computacional en el procesado de datos y también en lo relativo a la facilidad de programación.

Como objetivos específicos que se desean cumplir en las diferentes fases del presente Trabajo se pueden enumerar los siguientes:

1. Concebir la arquitectura HW más adecuada para la implementación de algoritmos criptográficos.

2. Elección e implementación de varios algoritmos criptográficos para dicha arquitectura.

3. Diseñar una aplicación genérica para verificar el funcionamiento de los algoritmos que sea ejecutada íntegramente en PC.

4. Crear un modelo para realizar co-simulación hardware con el objetivo de disminuir los tiempos de verificación obtenidos por la anterior aplicación.

5. Evaluar los resultados obtenidos.

## 4. Metodología

En el presente apartado, se realizará una descripción de la metodología seguida para la consecución de objetivos intermedios hasta lograr el principal. Se describirá el proceso seguido aunque será en el siguiente apartado donde realmente se profundizará en el funcionamiento de la aplicación.

### 4.1. Elección de la tecnología

Existen diversas alternativas para usar como co-procesador en un sistema para liberar de la carga computacional que supone un algoritmo criptográfico al procesador principal del sistema. Entre los distintos dispositivos existentes en el mercado las tres alternativas más interesantes son: DSP (Digital Signal Processor), GPU (Graphical Processing Unit) y FPGA (Field Programmable Gate Array).

El DSP es un microprocesador especializado en realizar determinadas tareas de procesado de señal digital como puede ser la compresión de video digital, de audio, implementar interfaces de comunicaciones... Su arquitectura está basada en reaprovechar el uso de un core formado por unidades aritméticas definidas (multiplicaciones de X bits, sumas...). Por ejemplo, en el caso de la arquitectura VLIW (Very Long Instruction Word) usada por Texas Instruments en la familia c64+ se dispone de dos multiplicadores y 6 ALUs (arithmetic logic units). Esta arquitectura permitiría realizar hasta 8 operaciones en un mismo ciclo de reloj (Texas Instruments, 2010) [21]. Estos recursos serán compartidos por todas las funciones que se ejecuten a lo largo del programa, de igual forma que los buses de acceso a memoria serán compartidos por el core del DSP y otros periféricos, obligando a establecer prioridades de acceso.

Se programan utilizando lenguaje C, lo que permite que resulte bastante sencillo realizar determinadas tareas, aunque para obtener un rendimiento adecuado y una optimización de recursos se requieren conocimientos sobre el uso de CACHE, DMA, los periféricos involucrados en la aplicación... en definitiva se requiere un conocimiento del hardware que compone internamente dicho DSP. En determinadas funciones críticas para el sistema en cuestiones de velocidad de ejecución, se pueden requerir conocimientos de un lenguaje de

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

programación específico del fabricante para optimizar el paralelismo en la ejecución de las instrucciones (Texas Instruments utiliza los denominados “intrinsics”) o el uso de lenguaje ensamblador.

La utilización del lenguaje C permite programar fácilmente rupturas del pipeline en el flujo de un programa condicional, lo cual es bastante difícil de implementar dentro de una FPGA. Esto no quiere decir que la ruptura del pipeline no afecte al rendimiento del DSP, ya que cualquiera de los 3 dispositivos planteados sufre una importante degradación de prestaciones con flujos condicionales, pero sin duda el DSP es el menos afectado y en el que resulta más sencillo implementar un código de este tipo.

La GPU al igual que el DSP presenta un set de recursos fijos que son utilizados por los programas que ejecutan, pero las GPUs están diseñadas para realizar un paralelismo de operaciones masivo, basándose su arquitectura en el uso de arrays de pequeños procesadores. Otro aspecto que optimiza la GPU es el acceso a memoria externa, puesto que su diseño está orientado a mover enormes cantidades de datos. Como su nombre indica son procesadores gráficos, por lo que son dispositivos especializados para realizar determinadas tareas. Si la aplicación que se va a desarrollar puede hacer un uso óptimo de las operaciones para las que está diseñada la GPU, podría ser utilizada para realizar tareas no relacionadas con el procesado de imagen o vídeo. Para su programación se usan principalmente dos lenguajes: CUDA (extensiones de C, C++ y Fortran para las GPUs del fabricante Nvidia) y OpenCL (u OpenGL en operaciones gráficas). La manera más sencilla de programar GPUs es mediante librerías de APIs, pero si éstas no proporcionan las operaciones necesarias para la aplicación que se deseé desarrollar existe la posibilidad de programar un set de APIs propio. Esta última tarea es bastante tediosa y complicada de realizar.

Frente a los dos dispositivos anteriores que se pueden considerar realmente como aceleradores SW destinados a acelerar ciertas aplicaciones computacionalmente intensivas, la FPGA proporciona un hardware configurable por el usuario. En las arquitecturas anteriores, el programa hacía uso de unos recursos ya existentes, en la FPGA el programador configura unos elementos lógicos básicos (LUTs en Xilinx y Logic Elements/Cells para Altera) que permiten construir los recursos que se deseen utilizar y configurar cómo se interconectarán entre ellos, para ajustarse perfectamente a las necesidades de la aplicación desarrollada. Esto conlleva de forma intrínseca una importante reducción del consumo. Para que sirva como ejemplo ilustrativo, se comentó anteriormente que el DSP de Texas Instruments (familia c64+)

disponía de 6 ALUs, en el caso de la FPGA se crearían las ALUs que se requieran y se estimen oportunas para la aplicación en concreto.

Esto permite una gran versatilidad y optimizar los recursos para el uso concreto al que estén destinados, aunque se debe tener en cuenta que para cada posible configuración o condición que se de en la aplicación se deberán destinar recursos. Si bien en ciertos casos se podrán reutilizar recursos, en la gran mayoría de los casos será una tarea compleja o degradará la frecuencia máxima alcanzable. Como el hardware ha sido configurado para una misión específica, no se llevan a cabo cargas de instrucciones (fetch) para determinar la operación a realizar como en el caso de los otros procesadores. Este hecho conlleva una importante reducción en cuanto a ciclos de ejecución se refiere, como se indica en el trabajo de Sirowy y Forin (2008) [17].

Si las operaciones matemáticas a realizar son especialmente complejas, el dispositivo más adecuado suele ser el DSP ya que dispone de los recursos necesarios para realizar este tipo de operaciones. Las FPGAs trabajan de manera óptima con operaciones de punto fijo mientras que para operaciones de coma flotante normalmente se requiere el uso de gran cantidad de lógica, no llegando a ser su implementación en cuanto a prestaciones comparable al DSP.

Por otro lado, las interconexiones en las GPUs suelen realizarse por PCI Express mientras que en los DSPs se limitan a los periféricos existentes en un modelo determinado. Este hecho limita el uso de GPUs a soluciones HW basadas en PC. Tanto las GPUs como los microprocesadores actuales utilizados en PCs no tienen un buen rendimiento en cuanto a consumo se refiere, por lo que no son adecuadas para dispositivos portátiles. Los DSPs como ya se ha comentado, pueden ser utilizados siempre y cuando presenten las conexiones que vaya a necesitar la aplicación por medio de sus puertos de entrada/salida y ofrezcan unas prestaciones en cuanto a velocidad adecuadas.

Las FPGAs disponen de una gran cantidad de pines de propósito general que pueden ser interconectados a prácticamente cualquier dispositivo siempre y cuando se respeten los niveles de tensión, por lo que resultan adecuadas para la mayoría de aplicaciones.

Tras analizar todo lo comentado, se pueden obtener las siguientes conclusiones:

- Mediante el uso de una FPGA y escogiendo el modelo adecuado, se usarán únicamente los recursos necesarios para la implementación del algoritmo o

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

algoritmos criptográficos que se escojan. Esta reducción de recursos lleva consigo una importante reducción de costes y consumo.

- El uso de una FPGA permite la posibilidad de conectarse a prácticamente cualquier dispositivo y posteriormente, implementar el interfaz que sea necesario.

- Independientemente del interfaz que se elija para realizar la comunicación con el procesador principal, la FPGA permitirá procesar en paralelo el número de bits que se estime oportuno. Debido a que es un dispositivo programable, permitirá realizar versiones posteriores modificando el código para aumentar o reducir el número de operaciones que se realizan en paralelo.

- Debido al grado de paralelismo de operaciones que permiten, las FPGAs pueden obtener importantes tasas de procesamiento de datos a frecuencias más bajas de funcionamiento que los otros dispositivos. Esto permite que el consumo de estos dispositivos sea inferior al de GPUs, CPUs o DSPs.

- Si los programadores no cuentan con la experiencia necesaria para programar el dispositivo de una manera eficaz usando lenguajes de descripción hardware, las herramientas que se utilizarán para crear el framework de intercomunicación del presente Trabajo permiten generar código de manera automática, lo que permitirá cumplir plazos de entrega ajustados.

En la siguiente gráfica se puede observar una comparativa extraída de [18] (Thomas et al, 2009), en la que comparan algoritmos de generación aleatoria de números (RNGs) optimizados para cada plataforma.

Table 6: Comparison of absolute performance and efficiency of RNGs across platforms.

|             | Performance (GSample/s)   |       |      |        | Efficiency (MSample/joule) |        |        |         |

|-------------|---------------------------|-------|------|--------|----------------------------|--------|--------|---------|

|             | CPU                       | GPU   | MPPA | FPGA   | CPU                        | GPU    | MPPA   | FPGA    |

| Uniform     | 4.26                      | 16.88 | 8.40 | 259.07 | 15.20                      | 140.69 | 600.00 | 8635.73 |

| Gaussian    | 0.89                      | 12.90 | 0.86 | 12.10  | 3.17                       | 107.52 | 61.48  | 403.20  |

| Exponential | 0.75                      | 11.92 | 1.29 | 26.88  | 2.69                       | 99.36  | 91.87  | 896.00  |

| Geo Mean    | 1.42                      | 13.75 | 2.10 | 43.84  | 5.07                       | 114.55 | 150.21 | 1461.20 |

|             | Relative Mean Performance |       |      |        | Relative Mean Efficiency   |        |        |         |

|             | CPU                       | GPU   | MPPA | FPGA   | CPU                        | GPU    | MPPA   | FPGA    |

| CPU         | 1.00                      | 9.69  | 1.48 | 30.91  | 1.00                       | 9.26   | 18.00  | 175.14  |

| GPU         | 0.10                      | 1.00  | 0.15 | 3.19   | 0.11                       | 1.00   | 1.95   | 18.92   |

| MPPA        | 0.67                      | 6.54  | 1.00 | 20.85  | 0.06                       | 0.51   | 1.00   | 9.73    |

| FPGA        | 0.03                      | 0.31  | 0.05 | 1.00   | 0.006                      | 0.05   | 0.10   | 1.00    |

Extraída de Thomas et al, 2009, pp. 9

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

En dichos resultados se observa como la FPGA resulta ser la mejor opción en términos de eficiencia de consumo y prestaciones. Pero en dicha tabla no aparece ninguna métrica relacionada con el precio de los dispositivos, y la FPGA empleada en estas medidas tiene un precio superior al resto de dispositivos. Debido a esto, resulta de vital importancia escoger una FPGA que cubra las necesidades del proyecto y se ajuste al presupuesto (no sobredimensionarla escogiendo un dispositivo mucho mayor al necesario y ceñirse a los requerimientos).

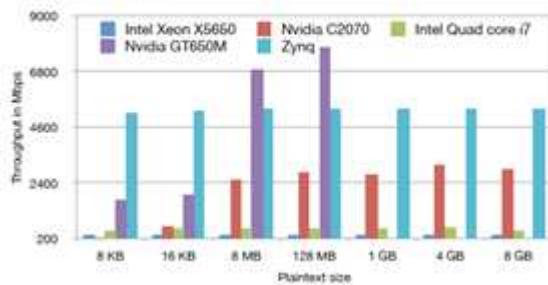

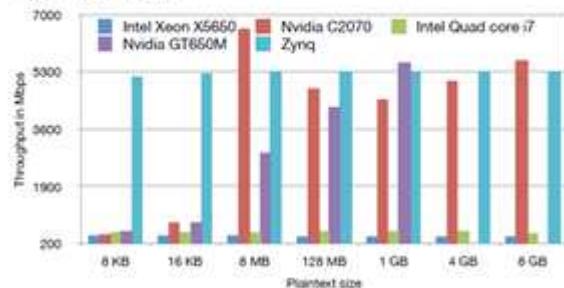

En el trabajo de Venugopal y Manikantan Shila (2013) [20], presentan las siguientes dos gráficas mostrando los resultados obtenidos para los algoritmos criptográficos TEA y XTEA:

Figure 5: Throughput (Mbps) comparison of TEA on CPU, GPU and FPGA

Extraída de Venugopal y Manikantan Shila (2013), pp.4

Figure 6: Throughput (Mbps) comparison of XTEA on CPU, GPU and FPGA

Extraída de Venugopal y Manikantan Shila (2013), pp.4

En dichas gráficas podemos observar cómo la solución basada en FPGA (Zynq de Xilinx) ofrece unos resultados más independientes del tamaño del texto aunque sea superada en prestaciones para algunos tamaños grandes. También se observa cómo dependiendo del algoritmo la GPU ganadora resulta ser un modelo u otro, mientras que la FPGA siempre mantiene unos buenos resultados.

## 4.2. Elección de los algoritmos

Los algoritmos criptográficos que se utilicen deberán ser adecuados al dispositivo que finalmente se ha elegido, la FPGA. De todo lo comentado en el apartado anterior se deduce que para que la implementación sea óptima, se deberá trabajar con algoritmos cuyas operaciones sean fácilmente paralelizables y se trate de operaciones no excesivamente complejas (descartando operaciones en coma flotante, divisiones, raíces cuadradas...). Sólo de esta forma realmente se beneficiará la implementación del uso de FPGAs.

Del algoritmo escogido se realizarán tres implementaciones. Primeramente, se establecerá el nivel en el que la seguridad de dicho algoritmo ha sido quebrantada (lo que comúnmente se conoce como que se ha “roto” el algoritmo). Una vez conocido dicho nivel, se realizará una versión en la zona límite de ruptura; otro superando dicha zona y por lo tanto, actualmente considerado inquebrantable y el último, un algoritmo con una configuración que se sabe de antemano que es vulnerable. Para las tres implementaciones se obtendrán resultados de ocupación en lógica del dispositivo, del número de operaciones por segundo que es capaz de realizar el algoritmo y del consumo correspondiente.

Como se ha comentado anteriormente, en el presente Trabajo se pretende crear un Framework que pueda ser utilizado para diversos algoritmos criptográficos de tal forma que las modificaciones a realizar para pasar de utilizar un algoritmo a otro sean mínimas. Para conseguir un framework fácilmente extrapolable, se parte del uso de algoritmos que emplean bloques de  $N$  bits en los que se divide el conjunto de datos inicial (ya sea un fichero de texto o de otro tipo). Esta condición se cumple para gran cantidad de algoritmos empleados en la criptografía como son las funciones resumen SHA1 (bloques de 512 bits), SHA256 (512 bits), SHA512 (1024 bits) o los cifradores de bloque DES (64 bits), IDEA (64bits)...

En este Trabajo se utilizarán los algoritmos SHA160, SHA256 y SHA512; ya que las modificaciones a realizar en el framework para integrar estos algoritmos serán suficientes para describir cómo incorporar otros algoritmos.

### 4.2.1. Funciones resumen SHA

Una función resumen (también llamadas funciones hash) de n-bit es una operación por la cual un mensaje de cualquier tamaño es convertido en otro mensaje de longitud n-bit. Normalmente son utilizadas para la protección de passwords y la generación de firmas digitales. Dentro de las propiedades que caracterizan una función resumen encontramos las comentadas en los apuntes de la asignatura de Criptografía y Mecanismos de Seguridad (Universidad Internacional de la Rioja, 2013) [22]:

- Debe requerir tiempos de computación muy elevados obtener dos mensajes que produzcan el mismo resumen.

- Tiene que ser computacionalmente intratable conseguir el mensaje en claro a partir del resumen.

- Igualmente, encontrar dos mensajes aleatorios que generen el mismo resumen debe ser computacionalmente intratable. Este concepto se conoce como colisión.

Actualmente se han encontrado colisiones en las implementaciones de las funciones hash MD4, MD5, SHA0 y SHA1. Para corregir dichos problemas de seguridad se han creado las versiones SHA2 y más recientemente, SHA3.

Las funciones SHA0 y SHA1 generan mensajes de 160 bits. SHA2 incluye una serie de importantes cambios respecto a sus predecesores así como el tamaño del resumen generado se incrementa hasta 224, 256, 384 o 512bits. Como ya se ha comentado los algoritmos escogidos para ser implementados en la FPGA han sido SHA1, SHA256 y SHA512. Sobre dichos algoritmos se realizará una comparativa en cuanto a velocidad, ocupación lógica y consumo. La elección de estos algoritmos viene condicionada por el hecho de que las operaciones que se realizan sobre el mensaje para obtener el resumen son muy sencillas y a que dividen los datos de entrada en bloques de longitud fija (N bits) para operar con ellos. Se trata de operaciones OR, XOR y AND a nivel de bit, desplazamientos, rotaciones y sumas que fácilmente pueden ser implementadas en una FPGA.

## 4.3. Implementación algoritmos

En este apartado se procederá a describir la implementación de los algoritmos criptográficos finalmente escogidos. Básicamente, se comentará el funcionamiento de cada algoritmo y los distintos módulos y operaciones que lo conforman. Dicha descripción será utilizada para entender el funcionamiento del modelo de referencia y de la instancia que se ejecutará en la FPGA.

### 4.3.1. SHA1

Sus siglas provienen de “Secure Hashing Algorithm”, es un algoritmo para crear resúmenes diseñado por “United States National Security Agency” (NSA) y publicado por el NIST. Supone una versión mejorada de su antecesor SHA0 y su primera publicación fue en 1995.

SHA1 genera resúmenes de 160 bits para mensajes de longitud de hasta  $2^{64} - 1$  bits. Su implementación es muy similar a la de MD4 o MD5, incluso compartiendo los mismo valores de inicialización. Estas similitudes provocaron, que tras demostrar que existían colisiones en el algoritmo MD5 en 2005, SHA1 comenzase a considerarse como una función resumen poco segura, ya que podría ser vulnerada en un futuro bajo un ataque similar. Microsoft anunció el pasado año que dejaría de aceptar certificados que utilizasen SHA1 después de 2016, tras un incidente ocurrido en Irán con un malware denominado Flame. Este malware explotaba una debilidad en MD5 junto a una vulnerabilidad en el Terminal Server, la conjunción de ambas vulnerabilidades permitía al atacante crear un certificado fraudulento firmado por Microsoft. Tras conocerse este hecho, Microsoft retiró inmediatamente el uso de MD5 en sus actualizaciones.

El funcionamiento del algoritmo SHA1 es el siguiente:

- El algoritmo trabaja sobre bloques de 512 bits, por lo que para completar el mensaje hasta alcanzar una longitud múltiplo de 512 bits se introduce relleno de la siguiente forma:

- Al final del mensaje se introducen 64 bits indicando la longitud real del mensaje.

- Entre el mensaje original y los 64bits anteriores, se introducen un '1' seguido de X ceros. Donde  $X = 448 - 1 - \text{longitud del mensaje}$ . 448 se obtiene de restar a 512 bits que debe ser la longitud final del mensaje de entrada al algoritmo, los 64bits destinados a la longitud real.

- Se divide el mensaje en N bloques de longitud 512bits. Donde  $N = \text{Longitud del mensaje} / 512$ .

- Se inicializan los cinco valores hash intermedios con las siguientes constantes:

$$A = 0x67452301$$

$$B = 0xEFCDAB89$$

$$C = 0x98BADCFC$$

$$D = 0x10325476$$

$$E = 0xC3D2E1F0$$

- Se aplica la función de compresión a cada bloque:

$h_i = H(h_{i-1}, M_i)$  es aplicado sobre el valor previo  $h_{i-1} = (A, B, C, D, E)$  y el bloque del mensaje.

- Después de ejecutar las N iteraciones el valor de  $h_n$  será el resumen final del mensaje obtenido de longitud igual a 160 bits.

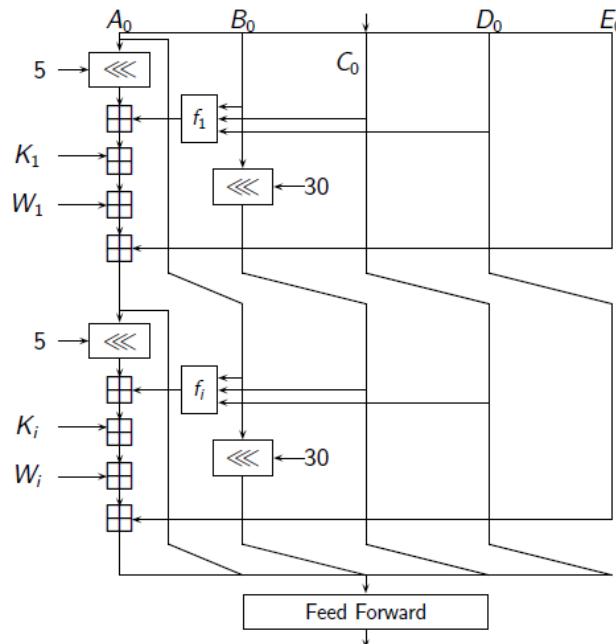

- La función de compresión sigue el siguiente esquema:

Figura extraída de Dunkelman (2012), pp.7

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

- Se divide el bloque  $M_i$  en 16 sub-bloques de 32bits:  $W_0, W_1 \dots W_{15}$

- Para cada  $t$  desde 16 a 79 se realiza la siguiente operación:

- $W_t = (W_{t-3} \text{ XOR } W_{t-8} \text{ XOR } W_{t-14} \text{ XOR } W_{t-16}) \lll 1$

NOTA: La rotación de un bit fue incluida en SHA1, en SHA0 no se realizaba y es la única diferencia entre ambos algoritmos.

- Se actualizan los valores  $A_0, B_0, C_0, D_0$  y  $E_0$  con  $h_{i-1}$

- Para cada  $t$  desde 0 hasta 79:

- $T = A_t \lll 5 + f_t(B_t, C_t, D_t) + E_t + W_t + K_t$

- $E_{t+1} = D_t, D_{t+1} = C_t, C_{t+1} = B_t \lll 30, B_{t+1} = A_t$

- $A_{t+1} = T$

- $A = A_0 + A80, B = B_0 + B80, C = C_0 + C80$

$D = D_0 + D80, E = E_0 + E80 \pmod{2^{32}}$

- La función  $f_t$  y los valores de  $K_t$  que se pueden observar en el esquema mostrado son:

$$\begin{aligned}

0 \leq t \leq 19: \quad f_t(X, Y, Z) &= XY \vee (\neg X)Z & K_t &= 5A827999 \\

20 \leq t \leq 39: \quad f_t(X, Y, Z) &= X \oplus Y \oplus Z & K_t &= 6ED9EBA1 \\

40 \leq t \leq 59: \quad f_t(X, Y, Z) &= XY \vee XZ \vee YZ & K_t &= 8F1BBCDC \\

60 \leq t \leq 79: \quad f_t(X, Y, Z) &= X \oplus Y \oplus Z & K_t &= CA62C1D6

\end{aligned}$$

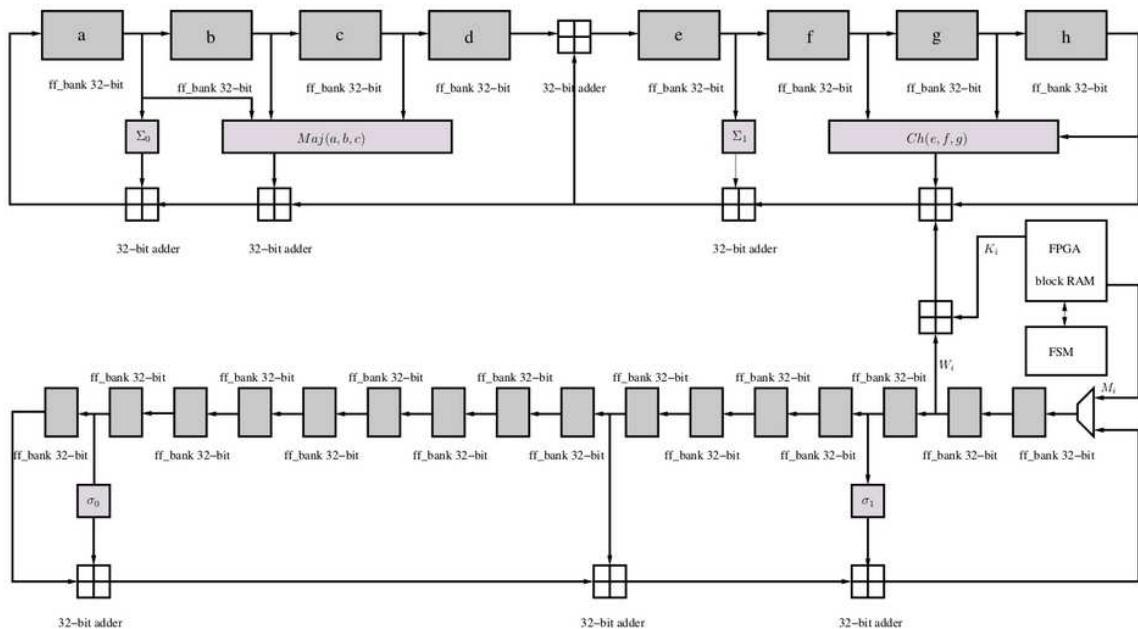

### 4.3.2. SHA256

En el algoritmo SHA-256 la función de compresión opera sobre bloques de mensaje de 512 bits y con valores de hash intermedios de 256 bits. Esencialmente se trata de un algoritmo de cifrado el cual cifra un valor de hash intermedio utilizando el bloque del mensaje como clave.

Para comenzar, el mensaje sobre el que se aplicará la función resumen debe ser extendido hasta formar un mensaje cuya longitud sea múltiplo de 512 bits. Posteriormente, dicho mensaje será dividido en bloques de 512 bits que se irán proporcionando a la función hash de uno en uno:

$$H(i) = H(i-1) + Cm(i)(H(i-1))$$

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

La anterior operación se realizará N veces. Siendo N = Longitud del mensaje /512. “C” es la función de compresión del algoritmo SHA256 y la suma se realizará a nivel de palabras de 32bits mod  $2^{32}$ .

El valor inicial  $H(0)$  es obtenido tomando la parte fraccional de las raíces cuadradas de los 8 primeros números primos. A continuación, se muestra la secuencia de palabras de 32bits que conforma dicho valor inicial:

$H(0)1 = 0x6a09e667$ ,  $H(0)2 = 0xbb67ae85$ ,  $H(0)3 = 0x3c6ef372$ ,  $H(0)4 = 0xa54ff53a$

$H(0)5 = 0x510e527f$ ,  $H(0)6 = 0x9b05688c$ ,  $H(0)7 = 0x1f83d9ab$ ,  $H(0)8 = 0x5be0cd19$

Para completar el mensaje hasta alcanzar una longitud múltiplo de 512bits se introduce relleno de la misma manera que para SHA1. Por ejemplo, para el texto “unir” la longitud del mensaje es 32bits, siendo la traducción a binario:

01110101 01101110 01101001 01110010

A continuación, añadiremos un ‘1’ seguido de X ceros, donde  $X = 448-1-32 = 415$ . Y al final se añadirá la longitud del texto de entrada (32 representado en 64bits). Así que el mensaje de entrada, tras insertar relleno sería:

01110101 01101110 01101001 01110010 1000...0000 000...100000

000...0000 → X ceros

000...100000 → Número 32 representado con 64bits.

Este algoritmo trabaja en sub-bloques de 32 bits por lo que habrá que dividir el mensaje sobre el que realizar el resumen en N-bloques de 512 bits y posteriormente, dividirlo en 16 sub-bloques de 32 bits.

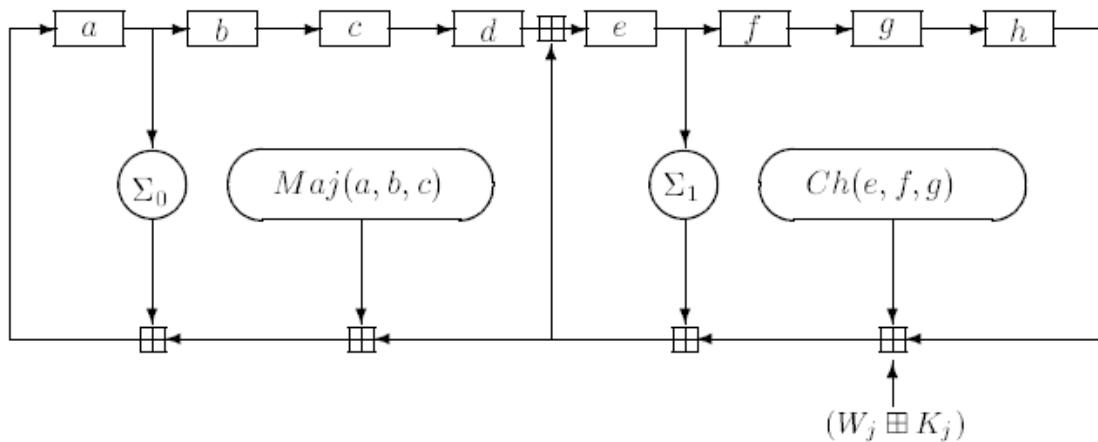

Para cada bloque de 512bits se realizarán las siguientes operaciones:

- Inicializar los registros a, b, c, d, e, f, g y h con el valor intermedio hash de la iteración anterior.

- $a \leftarrow H(i-1)0$ ;  $b \leftarrow H(i-1)1 \dots h \leftarrow H(i-1)8$

- Actualizar los registros aplicando la función de compresión de SHA256. Se realizan 64 veces las siguientes operaciones:

$$T1 \leftarrow h + \sum 1(e) + Ch(e,f,g) + Kj + Wj$$

$$T2 \leftarrow \sum 0(a) + Maj(a,b,c)$$

$$h \leftarrow g$$

$$g \leftarrow f$$

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

$$\begin{aligned}

f &\leftarrow e \\

e &\leftarrow d + T1 \\

d &\leftarrow c \\

c &\leftarrow b \\

b &\leftarrow a \\

a &\leftarrow T1 + T2

\end{aligned}$$

La función de compresión de SHA256 se representa en la siguiente figura:

Figura extraída de [15] (Anónimo), pp. 10

Se calcula el valor hash intermedio  $H(i)$

$$H1(i) \leftarrow a + H1(i-1) \dots H8(i) \leftarrow h + H8(i-1)$$

- El valor  $H8(N) = (H1(N), H2(N) \dots H8(N))$  compone el resumen resultado del mensaje de entrada  $M$ .

Las funciones utilizadas se definen de la siguiente forma:

$$Ch(x,y,z) = (x \text{ AND } y) \text{ XOR } (\neg x \text{ AND } z)$$

$$Maj(x,y,z) = (x \text{ AND } y) \text{ XOR } (x \text{ AND } z) \text{ XOR } (y \text{ AND } z)$$

$$\Sigma_0(x) = S^2(x) \text{ XOR } S^{13}(x) \text{ XOR } S^{22}(x)$$

$$\Sigma_1(x) = S^6(x) \text{ XOR } S^{11}(x) \text{ XOR } S^{25}(x)$$

$$\sigma_0(x) = S^7(x) \text{ XOR } S^{18}(x) \text{ XOR } R^3(x)$$

$$\sigma_1(x) = S^{17}(x) \text{ XOR } S^{19}(x) \text{ XOR } R^{10}(x)$$

Como se puede observar en el esquema un conjunto de 64 constantes son empleadas ( $K0 - K63$ ). Dichas constantes son las siguientes:

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

```

428a2f98 71374491 b5c0fbcf e9b5dba5 3956c25b 59f111f1 923f82a4 ab1c5ed5

d807aa98 12835b01 243185be 550c7dc3 72be5d74 80deb1fe 9bdc06a7 c19bf174

e49b69c1 efbe4786 0fc19dc6 240ca1cc 2de92c6f 4a7484aa 5cb0a9dc 76f988da

983e5152 a831c66d b00327c8 bf597fc7 c6e00bf3 d5a79147 06ca6351 14292967

27b70a85 2e1b2138 4d2c6dfc 53380d13 650a7354 766a0abb 81c2c92e 92722c85

a2bfe8a1 a81a664b c24b8b70 c76c51a3 d192e819 d6990624 f40e3585 106aa070

19a4c116 1e376c08 2748774c 34b0bcb5 391c0cb3 4ed8aa4a 5b9cca4f 682e6ff3

748f82ee 78a5636f 84c87814 8cc70208 90beffa a4506ceb bef9a3f7 c67178f2

```

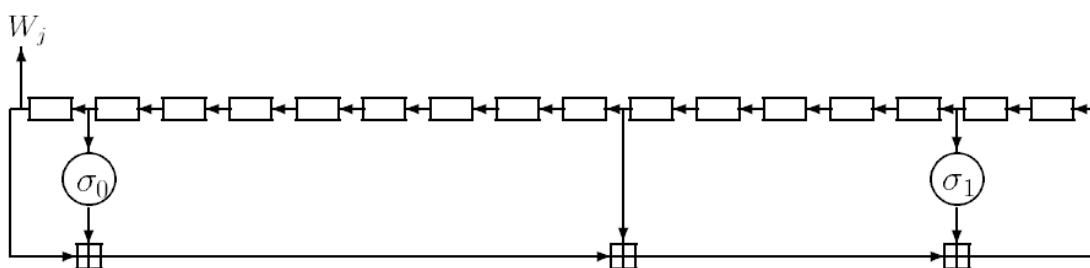

Por otro lado la obtención de  $W_j$  se realiza siguiendo este esquema:

Figura extraída de [15] (Anónimo), pp. 10

$$W_j = M_j(i) \text{ para } j = 0-15$$

Para  $j = 16$  hasta  $j=63$

$$W_j = \sigma_1(W_{j-2}) + W_{j-7} + \sigma_0(W_{j-15}) + W_{j-16}$$

### 4.3.3. SHA 512

El flujo de programa de la función hash SHA 512 es muy parecido al anterior pero dividiendo el mensaje en  $N$  bloques de 1024 bits para posteriormente, trabajar con sub-bloques de palabras de 64bits. Los valores hash intermedios son de 512 bits.

El relleno inicial se realiza de forma análoga al anterior algoritmo pero en esta ocasión, hasta conseguir un tamaño múltiplo de 1024. Las sumas se realizarán a nivel de palabras de 64 bits módulo  $2^{64}$ .

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

Los valores iniciales  $H(0)$  para la primera carga de los registros también son obtenidos mediante la parte fraccional de las raíces cuadradas de los 8 primeros números primos pero creando palabras de 64bits en lugar de 32.

$$\begin{aligned}

H_1^{(0)} &= 6a09e667f3bcc908 \\

H_2^{(0)} &= bb67ae8584caa73b \\

H_3^{(0)} &= 3c6ef372fe94f82b \\

H_4^{(0)} &= a54ff53a5f1d36f1 \\

H_5^{(0)} &= 510e527fade682d1 \\

H_6^{(0)} &= 9b05688c2b3e6c1f \\

H_7^{(0)} &= 1f83d9abfb41bd6b \\

H_8^{(0)} &= 5be0cd19137e2179

\end{aligned}$$

El relleno inicial se realiza de la misma manera que en el algoritmo anterior pero la longitud real del mensaje (sin relleno) se representa mediante 128bits. Por lo tanto, el relleno que se introducirá se conforma mediante un '1' seguido de X ceros. Siendo X = 896 – 1 – Longitud del mensaje de entrada.

Las funciones que se modifican respecto al anterior algoritmo son las siguientes:

$$\begin{aligned}

\Sigma_0(x) &= S^{28}(x) \oplus S^{34}(x) \oplus S^{39}(x) \\

\Sigma_1(x) &= S^{14}(x) \oplus S^{18}(x) \oplus S^{41}(x) \\

\sigma_0(x) &= S^1(x) \oplus S^8(x) \oplus R^7(x) \\

\sigma_1(x) &= S^{19}(x) \oplus S^{61}(x) \oplus R^6(x)

\end{aligned}$$

El bucle de la función de compresión se ejecuta 80 veces en lugar de las 64 iteraciones que se utilizan en SHA256. A su vez, el bucle para el cálculo de  $W_j$  varía para ejecutarse 64 veces en lugar de 32, quedando de la siguiente manera:

$W_j = M_j(i)$  para  $j = 0-15$

Para  $j = 16$  hasta  $j=79$ :

$$W_j = \sigma_1(W_{j-2}) + W_{j-7} + \sigma_0(W_{j-15}) + W_{j-16}$$

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

Las constantes de 64 bits utilizadas K0-K79 son las siguientes (hex):

```

428a2f98d728ae22 7137449123ef65cd b5c0fbcfec4d3b2f e9b5dba58189dbbc

3956c25bf348b538 59f111f1b605d019 923f82a4af194f9b ab1c5ed5da6d8118

d807aa98a3030242 12835b0145706fbe 243185be4ee4b28c 550c7dc3d5ffb4e2

72be5d74f27b896f 80deb1fe3b1696b1 9bdc06a725c71235 c19bf174cf692694

e49b69c19ef14ad2 efbe4786384f25e3 0fc19dc68b8cd5b5 240ca1cc77ac9c65

2de92c6f592b0275 4a7484aa6ea6e483 5cb0a9dcdbd41fdb4 76f988da831153b5

983e5152ee66dfab a831c66d2db43210 b00327c898fb213f bf597fc7beef0ee4

c6e00bf33da88fc2 d5a79147930aa725 06ca6351e003826f 142929670a0e6e70

27b70a8546d22fffc 2e1b21385c26c926 4d2c6dfc5ac42aed 53380d139d95b3df

650a73548baf63de 766a0abb3c77b2a8 81c2c92e47edaee6 92722c851482353b

a2bfe8a14cf10364 a81a664bbc423001 c24b8b70d0f89791 c76c51a30654be30

d192e819d6ef5218 d69906245565a910 f40e35855771202a 106aa07032bbd1b8

19a4c116b8d2d0c8 1e376c085141ab53 2748774cdf8eeb99 34b0bcb5e19b48a8

391c0cb3c5c95a63 4ed8aa4ae3418acb 5b9cca4f7763e373 682e6ff3d6b2b8a3

748f82ee5defb2fc 78a5636f43172f60 84c87814a1f0ab72 8cc702081a6439ec

90beffa23631e28 a4506cebde82bde9 bef9a3f7b2c67915 c67178f2e372532b

ca273eceeaa26619c d186b8c721c0c207 eada7dd6cde0eb1e f57d4f7fee6ed178

06f067aa72176fba 0a637dc5a2c898a6 113f9804bef90dae 1b710b35131c471b

28db77f523047d84 32caab7b40c72493 3c9ebe0a15c9bebc 431d67c49c100d4c

4cc5d4becb3e42b6 597f299cf657e2a 5fc6fab3ad6faec 6c44198c4a475817

```

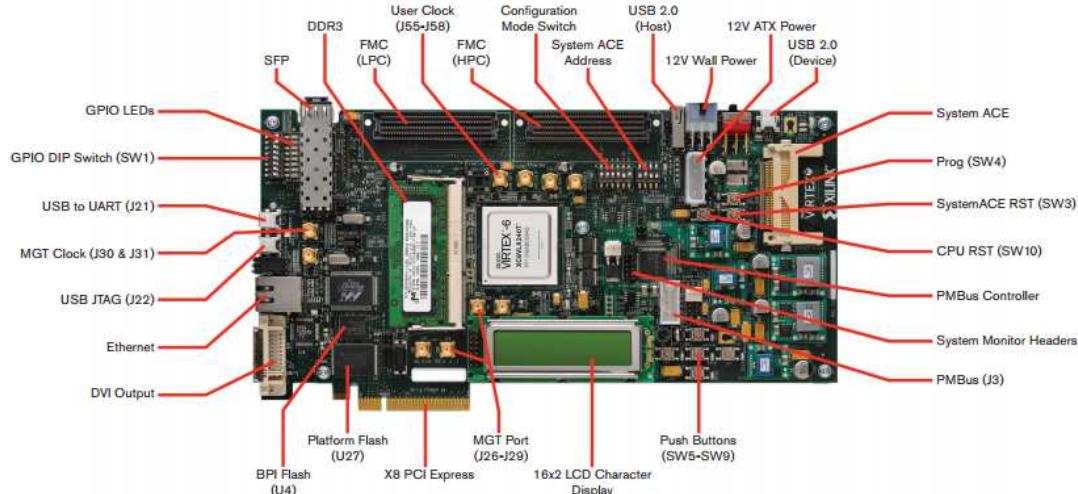

## 4.4. Elección de la plataforma

La aplicación ha sido desarrollada utilizando la tarjeta de evaluación ML605 diseñada por el fabricante de FPGAs, Xilinx. El objetivo de proporcionar este tipo de tarjetas es que posibles clientes puedan verificar el funcionamiento del dispositivo Virtex6 LX 240T y disponer de unos diseños de referencia a la hora de crear una PCB basada en tal FPGA. Dentro de las distintas familias de Xilinx, se trata de una FPGA optimizada para el uso de principalmente lógica distribuida, ya que no está destinada a tareas relacionadas con el uso de multiplicadores (familia SXT) ni a disponer de una gran conectividad serie (familia HXT). La lógica disponible en este dispositivo es enorme si consideramos los algoritmos que se van a implementar en ella y que requieren de pocos recursos, pero esto no supone ninguna limitación, ya que podremos verificar el funcionamiento del algoritmo en HW en esta tarjeta y una vez finalizada

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

la verificación, analizar los resultados obtenidos en la implementación en cuanto a uso de recursos y elegir una FPGA de menor tamaño para el diseño final.

Por supuesto, existen algunas diferencias entre los elementos lógicos que construyen internamente las distintas familias de dispositivos de Xilinx: Virtex-6, Spartan3, Spartan6, Serie-7... Por lo que idealmente, se debería elegir una tarjeta de evaluación de la familia que finalmente se vaya a utilizar, pero la elección de esta plataforma ha venido condicionada por la disponibilidad de conseguir una tarjeta de evaluación para el desarrollo del Trabajo Fin de Máster de manera gratuita.

Por otro lado, para facilitar la realización del presente Trabajo se buscó una tarjeta de evaluación que fuese compatible con la co-simulación HW en la herramienta System Generator, y de esta forma no vernos obligados a tener que desarrollar tareas de configuración extra.

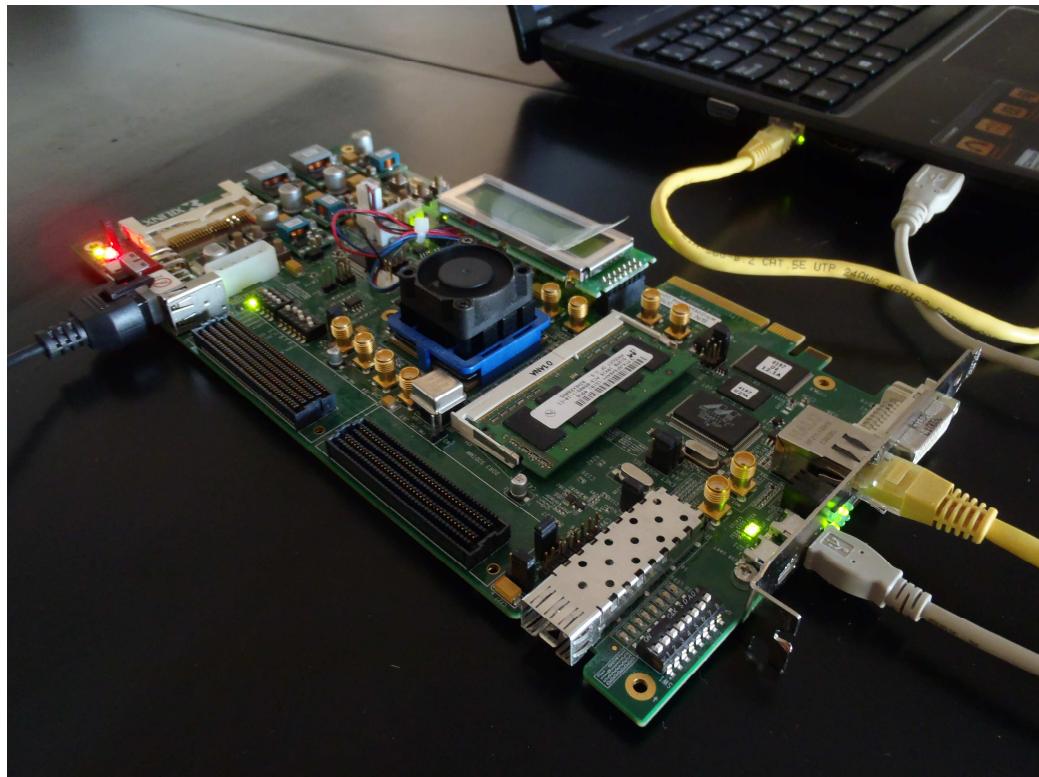

A continuación, se muestra la tarjeta de evaluación ML605 con sus componentes:

Para la realización de la co-simulación hardware será necesario hacer uso del conector USB (a través de la cadena JTAG) para configurar a la FPGA y del conector Ethernet, para llevar a cabo toda la transmisión/recepción de datos.

## 5. Contribución

La co-simulación Hardware es un proceso que ofrece como una de sus ventajas la capacidad de poder verificar el diseño implementado en Hardware sin la necesidad de tener que esperar a tener finalizado un prototipo del equipo. Las tarjetas de evaluación que proporcionan los fabricantes de FPGAs, en muchos casos intentan interconectar la FPGA con el mayor número de periféricos posible para permitir que puedan emplearse para verificar gran cantidad de diseños. En otros casos, existen varias tarjetas de evaluación de la misma FPGA pero destinadas a distintas funcionalidades, como puede ser procesado de vídeo, de audio, interconexión PCI... Pero la realidad demuestra que en gran cantidad de diseños la funcionalidad final no puede probarse con el hardware proporcionado o para probarlo se requiere la configuración de diversos periféricos que finalmente no serán incluidos en la PCB que se desarrolle, implicando un gasto de tiempo (y consecuentemente dinero) en el desarrollo de interfaces que luego no serán utilizados en la aplicación final. Gracias a la co-simulación hardware mediante la herramienta System Generator, la configuración de los dispositivos involucrados en la transferencia de datos se realizará de manera automática y totalmente transparente para el usuario.

Otra de las ventajas de la co-simulación Hardware reside en que permite que las entradas al sistema que se va a verificar sean generadas por el PC desde el entorno Simulink-Matlab, proporcionando una potencia matemática sin igual para introducir en las pruebas gran cantidad de vectores de test. De igual manera, los resultados que se generan en la FPGA pueden alimentar funciones en el PC que permitan analizar los resultados con todos los medios disponibles en el entorno Simulink-Matlab. De todo lo dicho se extrae que una gran ventaja que proporciona esta forma de verificación es el uso de la potencia de un PC a la hora de gestionar y analizar los datos de entrada/salida que se proporcionan o reciben a o desde el diseño que se ejecuta en la FPGA.

Cuando se diseñan e implementan diseños destinados a ser ejecutados en la FPGA, una de las fases clave del ciclo de desarrollo del código es la verificación de dicho diseño. Las depuraciones se realizan viendo señales digitales que son actualizadas en instantes infinitesimales, usando el PC a modo de analizador lógico sobre una ejecución virtual. Aunque se permite trabajar con entrada/salida de ficheros y se pueden llegar a realizar bancos de prueba muy versátiles, normalmente la realización de estos bancos de pruebas suele ser

bastante compleja y requiere de personal muy cualificado y con grandes conocimientos en lenguajes de descripción hardware. Por otro lado, debido a que estas simulaciones trabajan a nivel de bit sobre una lógica virtual, la velocidad de las simulaciones suelen ser muy dependientes de la plataforma de simulación de la que se disponga, pudiendo llegar a ser muy lentas.

La operación conjunta de Matlab, Simulink y System Generator permite realizar estos test-benches en un lenguaje más sencillo de utilizar y matemáticamente hablando, mucho más potente como es Matlab. Desde este punto de vista, únicamente se proporcionan mejores vectores de entrada y se optimiza el análisis de los resultados; pero se sigue teniendo el problema de la velocidad en la ejecución. La solución a este problema reside en ejecutar la parte correspondiente al código de la FPGA realmente en el Hardware y la generación y análisis de resultados en el PC, lo cual conducirá a una importante reducción en cuanto a tiempos de simulación se refiere.

Aprovechando la cualidad existente en gran cantidad de algoritmos criptográficos de trabajar con bloques de longitud fija, se realizará un framework en el que simplemente con la sustitución del bloque que contiene al algoritmo y la modificación del valor de la variable en el que se indica el tamaño de bloque usado, se pueda ejecutar otro algoritmo dentro del mismo proyecto. Esto supone claras ventajas en cuanto al mantenimiento y reusabilidad del código en la realización de bancos de pruebas, lo cual conlleva una importante reducción del tiempo empleado en la implementación de las pruebas de verificación. Por otro lado, facilita la separación de entornos (desarrollo y pruebas), ya que el algoritmo a depurar será tratado como una caja negra sin necesidad de que la persona que realice las pruebas deba saber cómo se encuentra implementado.

## 5.1. Requisitos iniciales

Para el diseño de la aplicación se han considerado una serie de requisitos que permitan conseguir de una manera óptima los objetivos planteados.

En primer lugar, los algoritmos criptográficos que se utilicen deberán ser adecuados para su correcta implementación en una FPGA. Para llevar a cabo dicha elección, se debe optar por la lectura de la literatura existente sobre implementaciones óptimas de diversos algoritmos en FPGAs (Ver apartado 2, Marco Teórico). Para posibilitar la realización de un Framework lo más general posible, dichos algoritmos deberían trabajar sobre bloques de entrada de longitud

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

fija y llevar a cabo todas las operaciones que lo diferencien de otros algoritmos en su interior y de una manera transparente al Framework (ya que serán tratados como cajas negras).

Debido a que la tecnología empleada para la realización de este Trabajo no posibilita un intercambio de señales de control entre la FPGA y el PC de una manera eficiente, cuanta menos lógica de control que suponga intercambio de información entre ambos dispositivos se realice, más fácil será la integración con el Framework. Esto no es aplicable a la transferencia de grandes volúmenes de datos de entrada y salida mediante los búferes que proporcionan las herramientas y que se encuentran destinados a tal propósito.

Por otro lado, en la Aplicación que se desarrolle, deberán estar claramente identificadas desde el diseño inicial las partes que se ejecutarán en cada dispositivo (en PC o en FPGA).

## 5.2. Tecnologías empleadas

En el apartado “4.1 Elección de la tecnología” se justificó la elección de las Tecnologías empleadas en el presente Trabajo Fin de Máster, en los siguientes apartados se describen aspectos importantes de las herramientas utilizadas.

En la aplicación implementada interactúan una serie de herramientas de distintos fabricantes que han decidido colaborar para desarrollar una solución conjunta que simplifique el proceso de diseño, desarrollo y depuración de proyectos basados en FPGA.

### 5.2.1. Herramientas para el desarrollo en PC

Mathworks es una compañía líder en el desarrollo de software para cálculo matemático para ingenieros y científicos. Cuenta con 30 años de experiencia en este campo y más de 3000 trabajadores distribuidos a lo largo de 15 países. De esta compañía se utilizará el software sobre el que se cimienta todo este trabajo, las herramientas destinadas al Diseño basado en modelos Matlab y Simulink.

Matlab es un entorno interactivo para el cálculo numérico basado en un lenguaje de alto nivel propio. Se trata de una potente herramienta para analizar datos, desarrollar algoritmos y crear

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

modelos o aplicaciones. Es ampliamente utilizada en cálculos, principalmente en sistemas de control automáticos y en procesado de señal, ya que proporciona un lenguaje muy sencillo para elaborar programas matemáticos. Matlab posee una gran cantidad de toolboxes (librerías) específicas para distintas áreas de trabajo como puede ser procesado de señal, procesado de imagen...

Simulink es un producto que se ejecuta sobre Matlab, que proporciona un entorno de interactivo y gráfico para el modelado, la simulación y análisis de sistemas dinámicos. Permite elaborar prototipos virtuales de una manera rápida para explorar los diseños a cualquier nivel de detalle. Simulink incluye una librería de bloques predefinidos para ser utilizados en la construcción de modelos gráficos de sistemas arrastrando y soltando (drag-and-drop) los distintos elementos que los compongan. Soporta sistemas lineales y no lineales, modelado basado en muestreo, en captura continua o un híbrido de ambos. Como se trata de un producto totalmente integrado con Matlab los datos pueden ser fácilmente compartidos entre ambos programas proporcionando a la aplicación desarrollada, toda la potencia computacional que proporcionan las funciones propias de Matlab. Los bloques que utiliza Simulink son proporcionados por los denominados "BlockSets". Existen gran cantidad de "BlockSets" que contienen elementos especializados para determinadas tareas, como puede ser "Aerospace BlockSet", que contiene bloques para modelar y simular sistemas de propulsión, aeronáuticos y aeroespaciales.

System Generator es una herramienta de modelado a nivel de sistema que facilita el diseño hardware sobre FPGA. Puede definirse como un BlockSet que extiende la funcionalidad de Simulink al ámbito del desarrollo hardware por medio de una serie de bloques predefinidos que son directamente sintetizables en una FPGA. Dicho de otro modo, permite de una manera rápida y visual desarrollar un diseño sobre Simulink que pueda ejecutarse posteriormente de una manera directa en una FPGA. Tras validar el diseño, simplemente apretando un botón de la herramienta se generará un bitstream de configuración de la FPGA con la misma funcionalidad que la simulada. Una de las ventajas que proporciona System Generator es el uso de las denominadas, "black boxes". Una "black box" es un módulo realizado en lenguaje de descripción hardware (VHDL o Verilog) que es importado desde System Generator para generar un bloque que pueda ser utilizado desde el entorno gráfico. Esto permite que cualquier algoritmo criptográfico que se desarrolle pueda ser convertido en un bloque y sea utilizado por un módulo mayor para crear el modelo de un sistema en Simulink. O siendo más ambiciosos, esto permite desarrollar en lenguaje de descripción hardware cualquier bloque que se necesite en la aplicación.

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

Realmente con los bloques básicos que proporciona System Generator, se puede llegar a crear con más o menos esfuerzo cualquier diseño digital. Pero si se cuenta con personal experimentado que conozca cómo implementar y optimizar dicha lógica en la FPGA, el resultado final respecto a la generación automática de código permitirá obtener mejores resultados en cuanto a reducción de la lógica empleada y en aumento de la frecuencia máxima de funcionamiento. Por otro lado, si el personal no tiene grandes conocimientos en programación de dispositivos lógicos, con System Generator y haciendo uso de sus componentes básicos, se conseguirá obtener un producto de una manera muy rápida gracias a que todas las operaciones se pueden realizar mediante un interfaz gráfico.

System Generator es una herramienta integrada en el entorno de desarrollo ISE del fabricante de FPGAs Xilinx. Como es obvio, esta herramienta sólo es válida para FPGAs de este fabricante. Si se opta por usar dispositivos lógicos del otro gran fabricante (Altera), se deberá usar la herramienta equivalente llamada Altera DSP Builder.

La versión finalmente empleada de Matlab es R2007a y de System Generator la asociada al entorno ISE12.3.

## 5.2.2. Herramientas para el desarrollo en FPGA

System Generator convierte los bloques empleados en el modelado del diseño a una traducción directa en una serie de ficheros escritos en lenguaje de descripción hardware que describen de forma inequívoca el funcionamiento de dichos bloques. Posteriormente, System Generator cede el control del resto de procesos que se deben realizar hasta generar el bitstream de configuración de la FPGA al entorno ISE de Xilinx.

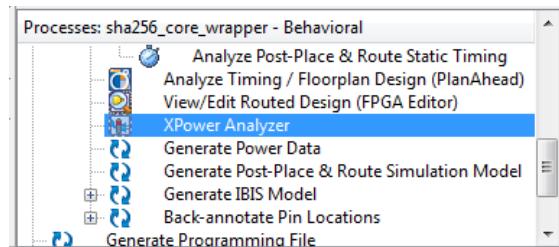

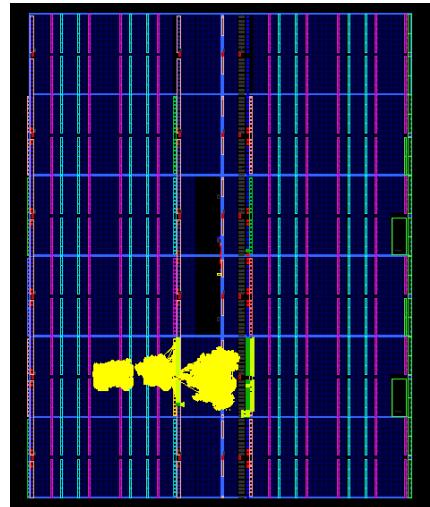

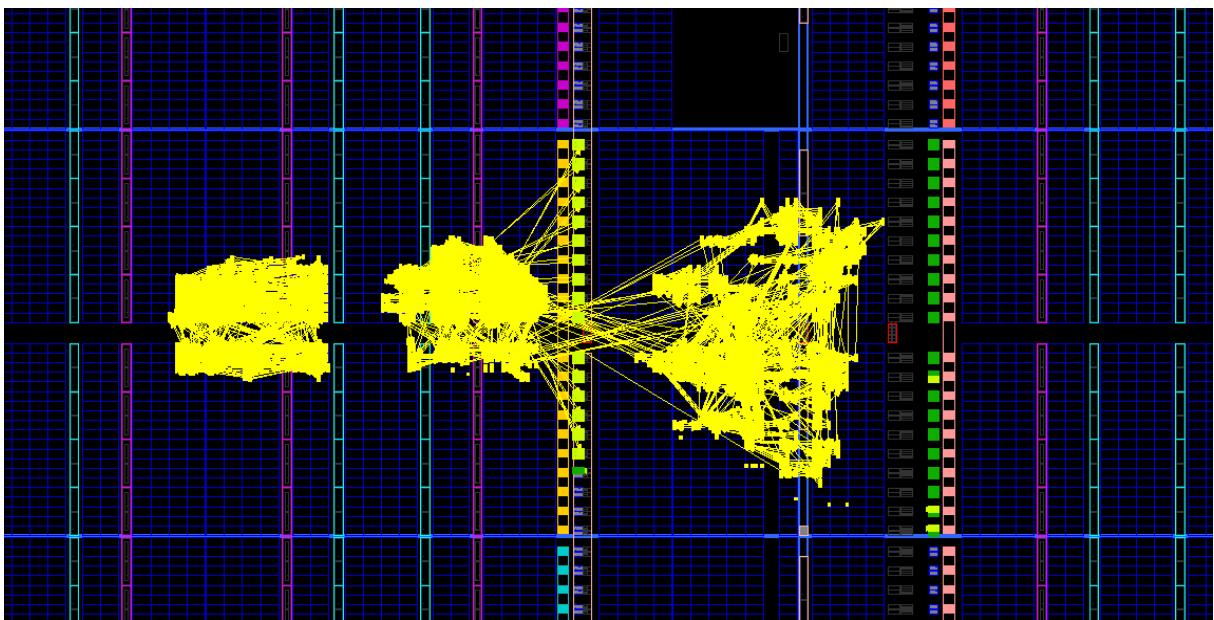

La primera tarea a realizar será la síntesis de los ficheros de descripción hardware previamente generados para obtener a la salida de este proceso una “netlist” que indique los componentes básicos a utilizar (multiplexores, sumadores, contadores, memorias...) y las interconexiones entre estos componentes.

Posteriormente, se realizará el proceso denominado en inglés “map” que realiza una traducción de esos componentes detectados, a una implementación en la lógica que utiliza la FPGA según la tecnología que se emplee para su construcción. En otras palabras, traduce la “netlist” al conjunto de elementos lógicos de nivel más bajo que se interconectarán para realizar las funciones indicadas. Una vez determinados los elementos de bajo nivel que se emplearán en la FPGA y cómo se interconectan, se procede a situarlos dentro de la lógica de

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

la FPGA de tal manera que se cumplan los requisitos de frecuencia máxima de funcionamiento impuestos (timing constraints). A este proceso se le denominada “Place & Route” y una vez finalizado, si se cumplen los requisitos de frecuencia de funcionamiento, se podrá generar finalmente el bitstream de configuración de FPGA. Este bitstream de configuración será el medio por el que se programará la funcionalidad de la FPGA cada vez que se encienda de nuevo el equipo (o tarjeta de evaluación) ya que se trata de un dispositivo volátil. Cada vez que se deseen realizar modificaciones en el proyecto, lógicamente también será necesario reconfigurar el dispositivo.

Para verificar el correcto funcionamiento de los algoritmos criptográficos antes de ser integrados en el sistema de co-simulación Hardware como cajas negras de System Generator, se realizarán unas breves simulaciones en PC. Otro objetivo de estas simulaciones es proporcionar tiempos de ejecución que sirvan para compararlos con el sistema propuesto de co-simulación HW durante pruebas exhaustivas de funcionamiento.

Para la realización de estas pruebas se utilizó el entorno de simulación Modelsim SE de Mentor Graphics y el simulador ISIM. ModelSim destaca entre sus competidores (como por ejemplo, Riviera de la compañía Aldec) por su velocidad, pero también tiene un coste bastante mayor.

Existen diversas configuraciones de esta herramienta que permiten reducir su precio de adquisición a expensas de reducir la velocidad de simulación y prescindir de algunas características avanzadas, como puede ser la capacidad multi-lenguaje. Por otro lado, existen versiones específicas para los principales fabricantes de FPGAs (Altera y Xilinx) que prescinden de algunas características de la versión SE y son bastante más lentas, pero tienen una importante reducción de precio.

El simulador ISIM se encuentra integrado en el entorno de desarrollo ISE de Xilinx, y su uso no requiere el pago de ninguna licencia extra.

Las versiones utilizadas en el presente trabajo de los productos comentados en este apartado son ISEv12.3 y ModelSim SE10.d.

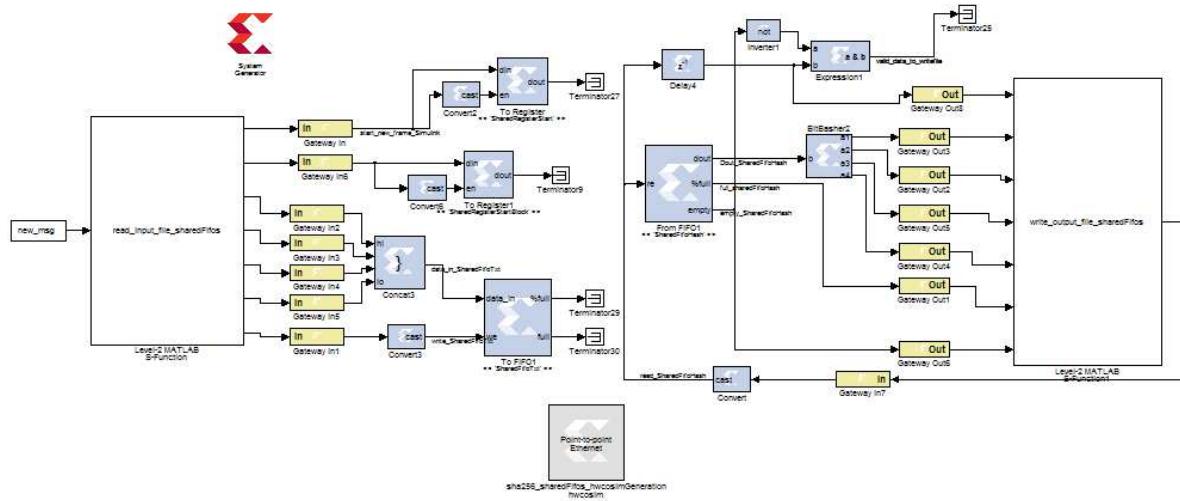

### 5.2.3. Interfaz de comunicación PC-FPGA

Para poder realizar la comunicación entre el PC y la FPGA se debe hacer uso de ciertos drivers en el PC y se requiere implementar en la FPGA la lógica necesaria para la recepción y transmisión de los datos. Además, se deberán configurar los periféricos de la tarjeta de evaluación que se utilicen para transmitir los datos desde los conectores de la tarjeta en sí a los pines de entrada/salida de la FPGA (en el caso de la aplicación desarrollada en este Trabajo, todo lo necesario para establecer una comunicación vía Ethernet o JTAG). Estas tareas son realizadas de forma transparente al programador por la herramienta System Generator, siempre y cuando se utilice una de las tarjetas de evaluación soportadas por la herramienta. Existe la posibilidad de utilizar otras tarjetas (siempre y cuando se cumplan ciertos requisitos) realizando algunas tareas de configuración extra.

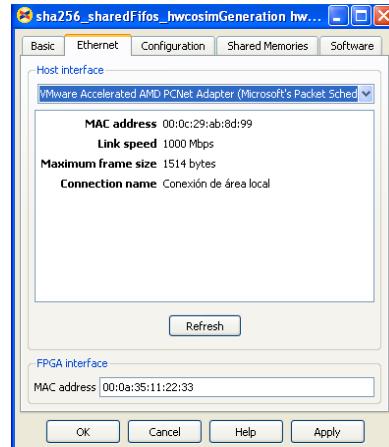

La mayoría de estas tarjetas ofrecen dos modos de transmisión: a través del JTAG o por medio de Ethernet. El primer modo es bastante sencillo de utilizar pero la frecuencia de funcionamiento del sistema (la del JTAG) es bastante baja, por lo que no obtenemos ninguna mejora frente a la simulación convencional. El segundo modo de funcionamiento es el que realmente proporcionará una frecuencia de funcionamiento real, ya que se podrá transmitir datos hasta una frecuencia de 1Gbps que serán procesados por la FPGA a la máxima frecuencia de funcionamiento para la cual haya sido diseñado el sistema. Para permitir este modo de funcionamiento de manera continua, se requerirá el uso de unas memorias dentro de la FPGA que son configuradas como “espejo” de unas memorias equivalentes en el PC. Este tipo de memorias se conocen como “Shared Memories” y su funcionamiento será explicado con mayor detalle en otros apartados.

### 5.3. Descripción de la aplicación

Será en este apartado donde se tratará la aplicación propiamente dicha, desglosándola en las diferentes partes que la componen y explicando la metodología de trabajo seguida.

La aplicación desarrollada consta de varias partes claramente diferenciadas y para su realización se han ido completando una serie de hitos intermedios que pueden ser utilizados según el criterio del usuario para cumplir distintos objetivos.

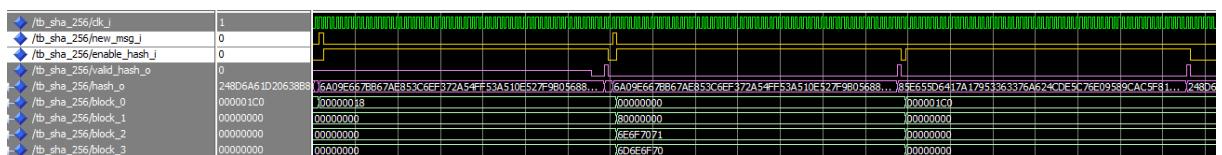

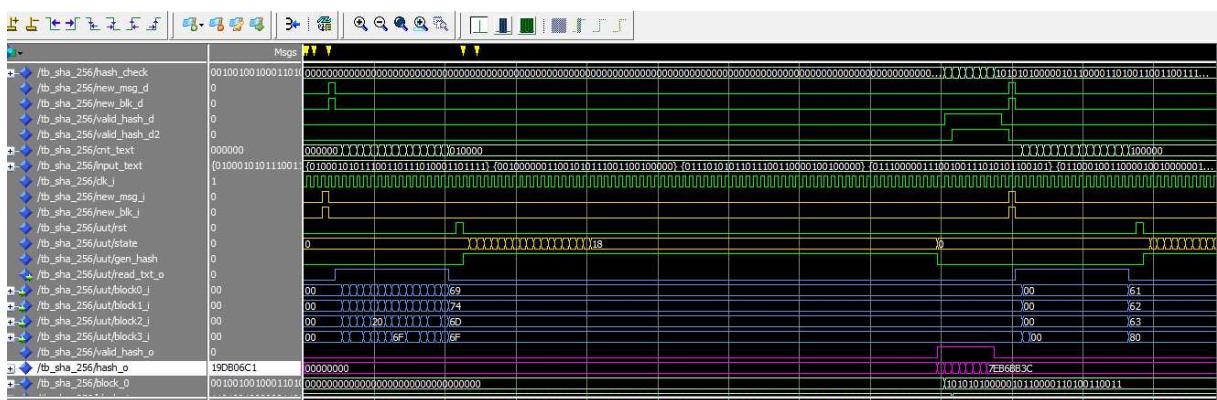

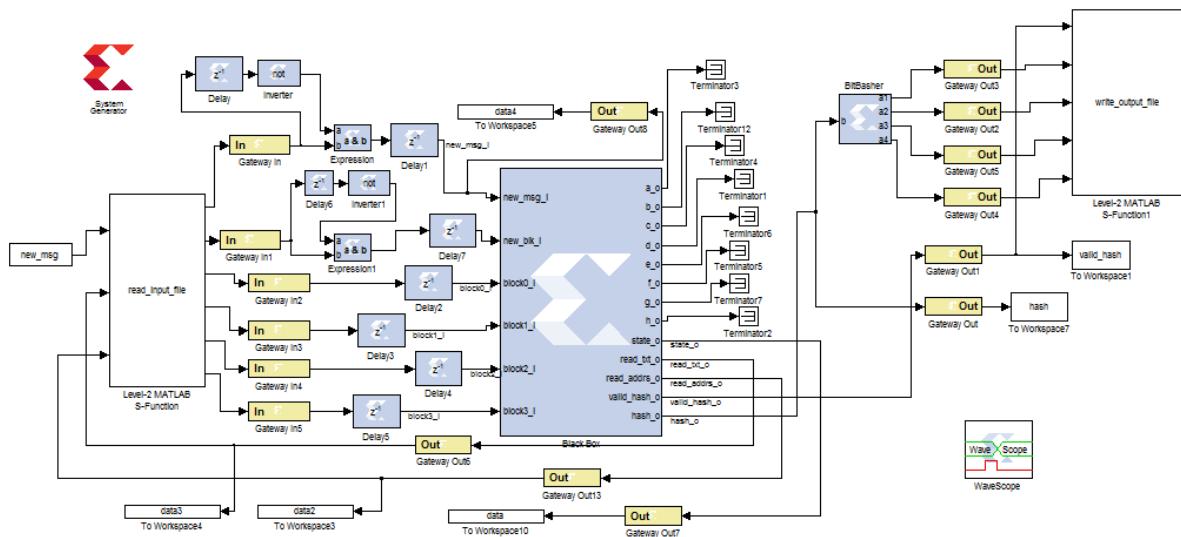

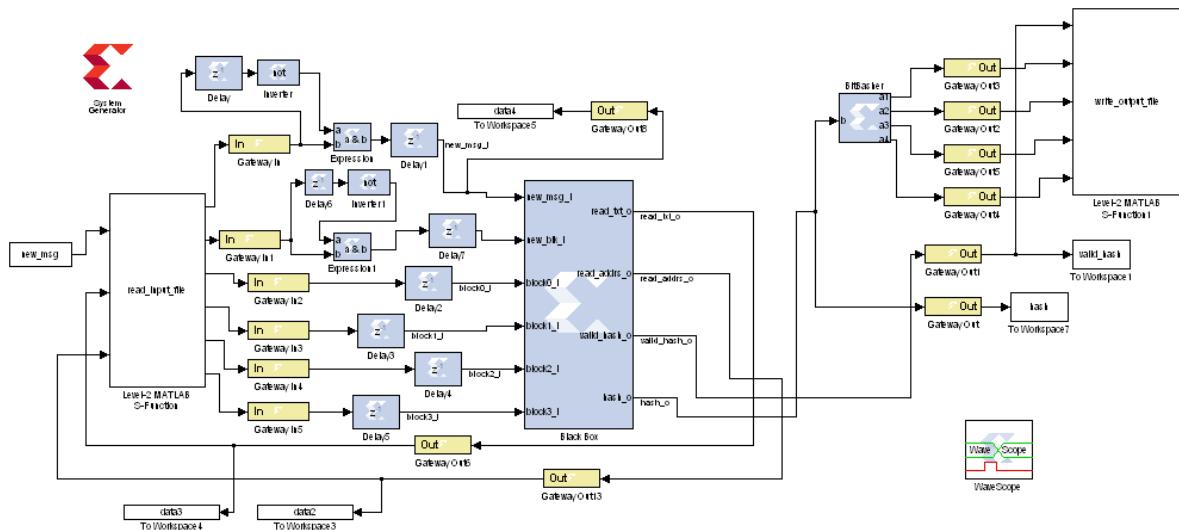

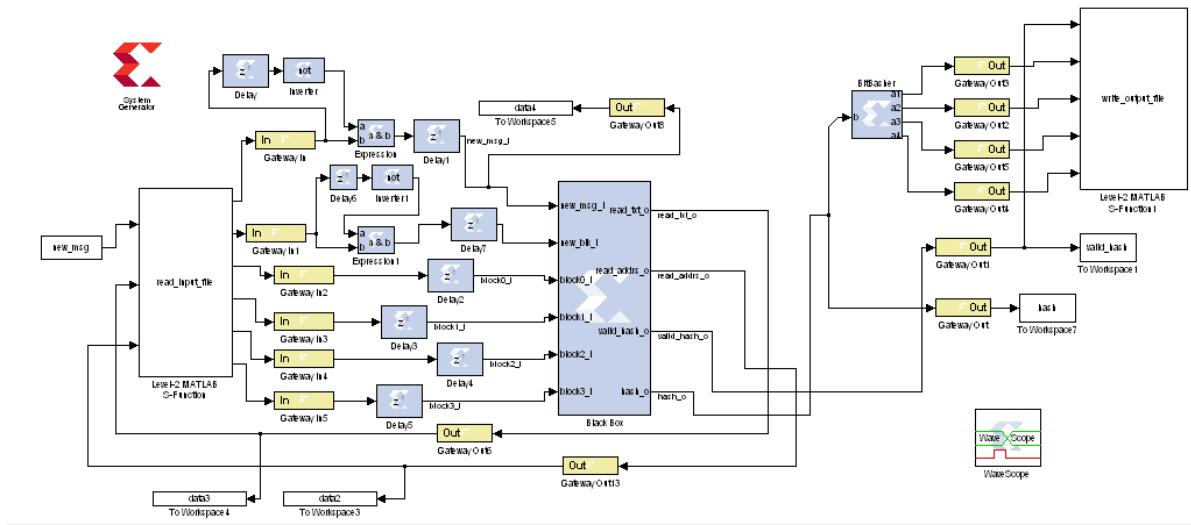

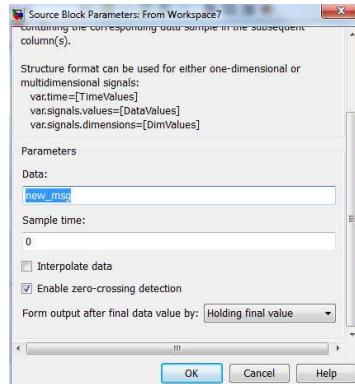

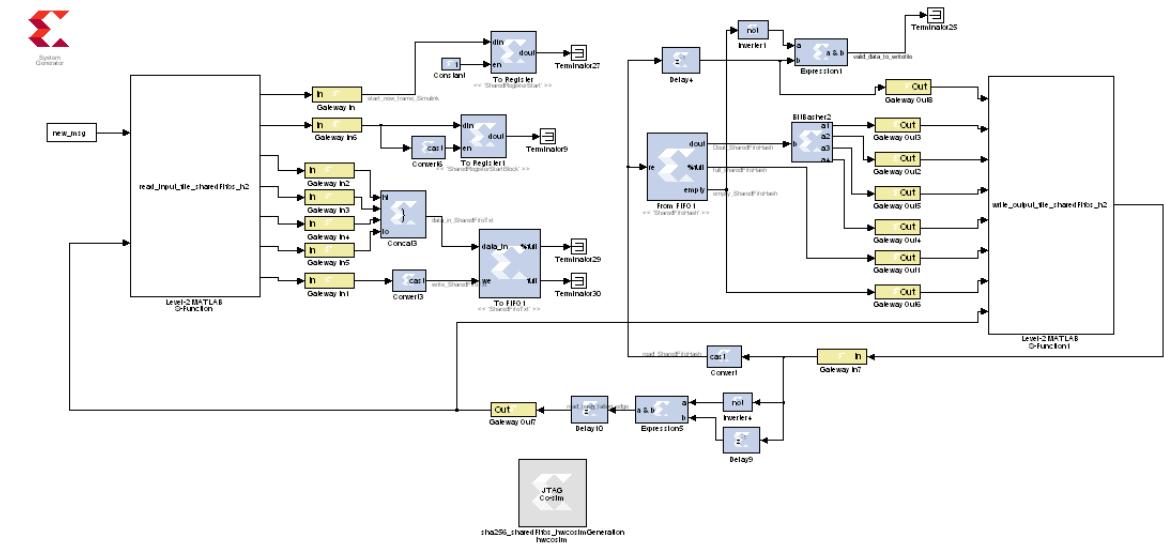

El primer gran hito planteado fue el diseño de una aplicación que se ejecutase íntegramente en el PC pero teniendo en mente que posteriormente diversas partes se ejecutarían en dispositivos distintos (PC y FPGA). Para asegurar este requisito, lo más sencillo es definir claramente las entradas y salidas del sistema ya que éstas serán ejecutadas en el PC. El algoritmo será siempre tratado como una "black box", de forma que para la aplicación se trate simplemente de otro bloque con una serie de entradas y salidas. En este primer hito el algoritmo se alimenta directamente de una función de Matlab que lee un fichero de texto de entrada y se lo proporciona al algoritmo en bloques de 32bits. Será cada algoritmo el que determinará mediante una señal de lectura cuántos bloques desea leer y en qué instantes. De manera equivalente, las salidas del algoritmo se proporcionan a una función de Matlab en bloques de 32 bits y se almacenan en un fichero de salida. La limitación del uso de buses de 32bits es impuesta por System Generator, ya que no permite instanciar memorias con datos de tamaño superior.

En un segundo hito, la lectura/escritura de datos entre el algoritmo y las funciones de Matlab no se realizará directamente, si no que se intercalarán entre las funciones y el algoritmo, FIFOs que almacenen los datos entre los distintos procesos. Para implementar dichas FIFOs se emplearán los componentes denominados por System Generator "Shared Memories". Cada uno de estos componentes consiste realmente en una pareja de memorias. Cada memoria es un espejo de la otra para un dominio de trabajo distinto, pueden ser vistas como una especie de memoria doble puerto en la que cada puerto estará conectado a un dominio distinto. Un dominio será el encargado de escribir en dicha memoria y en el otro se leerán los datos. Esto posibilita que un dominio sea el entorno de trabajo en el PC y otro, la FPGA. En este hito de momento todo se ejecutará en el PC con vistas a depurar más fácilmente los fallos que puedan surgir.

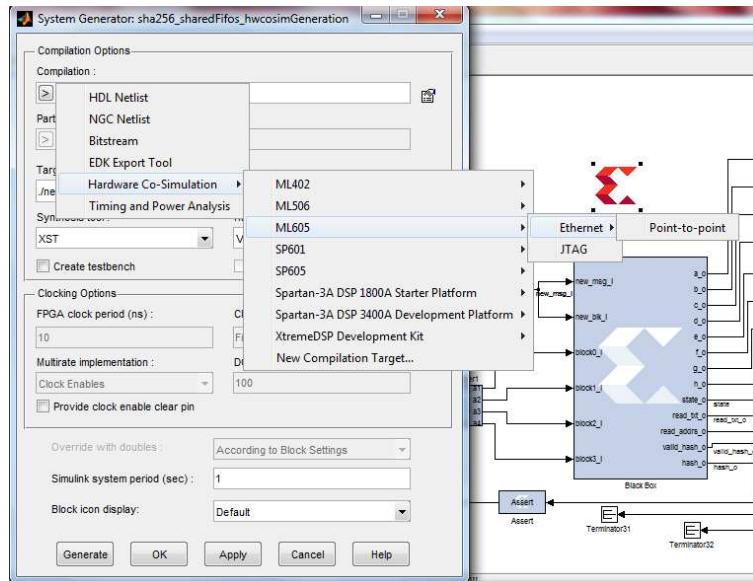

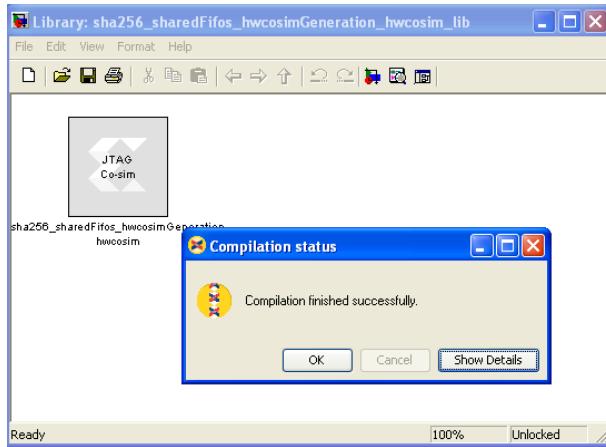

En el tercer y último hito, se utilizará la división de entornos realizada en el anterior hito para asignar a cada dominio un dispositivo. Se procederá a generar un componente que sea ejecutable en la FPGA, se configurará la FPGA y se ejecutará la aplicación. La gestión de entrada/salida la realizará el PC y el algoritmo se ejecutará en la FPGA. Se realizará una primera versión ejecutando la aplicación a través del JTAG a una frecuencia reducida debido a su facilidad de configuración, y una vez verificado el funcionamiento sobre placa, se procederá a incrementar la velocidad de ejecución mediante un interfaz de comunicación de datos a través de ethernet Gigabit.

### 5.3.1. Modelos de referencia

En el presente apartado se describirán los modelos de referencia que se han utilizado para corroborar que los algoritmos criptográficos implementados funcionan correctamente. Inicialmente se consideró la implementación de los algoritmos escogidos en un lenguaje de alto nivel para verificar que la implementación de los algoritmos en lenguaje de descripción hardware se realizaba correctamente, pero viendo la gran cantidad de software libre existente se desestimó su implementación. Carece de sentido implementar un modelo de referencia sujeto a errores de codificación y tiempo de implementación y depuración asociado cuando existen soluciones libres que han sido ampliamente probadas.

Todos los pasos intermedios que han sido realizados durante la elaboración de la aplicación hasta su finalización, han sido verificados comprobando que las salidas obtenidas en cada proceso se correspondían con unas referencias iniciales. Dichas referencias fueron obtenidas del banco de pruebas implementado en lenguaje de descripción hardware que está incluido junto a cada algoritmo en los paquetes de libre distribución. En todo momento se ha asegurado que las modificaciones que se iban realizando no afectaban al correcto funcionamiento del algoritmo.

Existe código libre en lenguaje Matlab, como el encontrado en la referencia [26] (Simon, 2012), que podría ser incorporado en futuros trabajos sobre el framework desarrollado para comprobar los resultados de manera automática. También existen soluciones online que proporcionan el resumen de un texto o fichero de entrada para diferentes tipos de algoritmos [27] ([hash.online-convert.com](http://hash.online-convert.com)).

Implementación basada en co-simulación HW de un algoritmo criptográfico en una FPGA

## 5.3.2. Algoritmos FPGA

La implementación de los algoritmos escogidos se puede realizar siguiendo las indicaciones que proporciona la descripción del apartado “4.3 Implementación de algoritmos/Funciones resumen”. Como ya se comentó, existen diversas implementaciones disponibles como código libre y se han realizado diversos trabajos sobre implementaciones óptimas de estos algoritmos, por lo que el diseño de una nueva implementación de estos algoritmos no es objetivo del presente Trabajo. Por ello, se describirán brevemente las implementaciones utilizadas y se indicará el link al sitio WEB de distribución de SW libre donde se obtuvo cada implementación. Debido a que dichas implementaciones no son directamente portables al framework de la aplicación desarrollada también se comentarán las modificaciones realizadas sobre cada implementación para permitir la integración.

Para cada algoritmo se explicarán aspectos claves de su implementación y cómo se ha realizado su verificación.

### 5.3.2.1. SHA 256

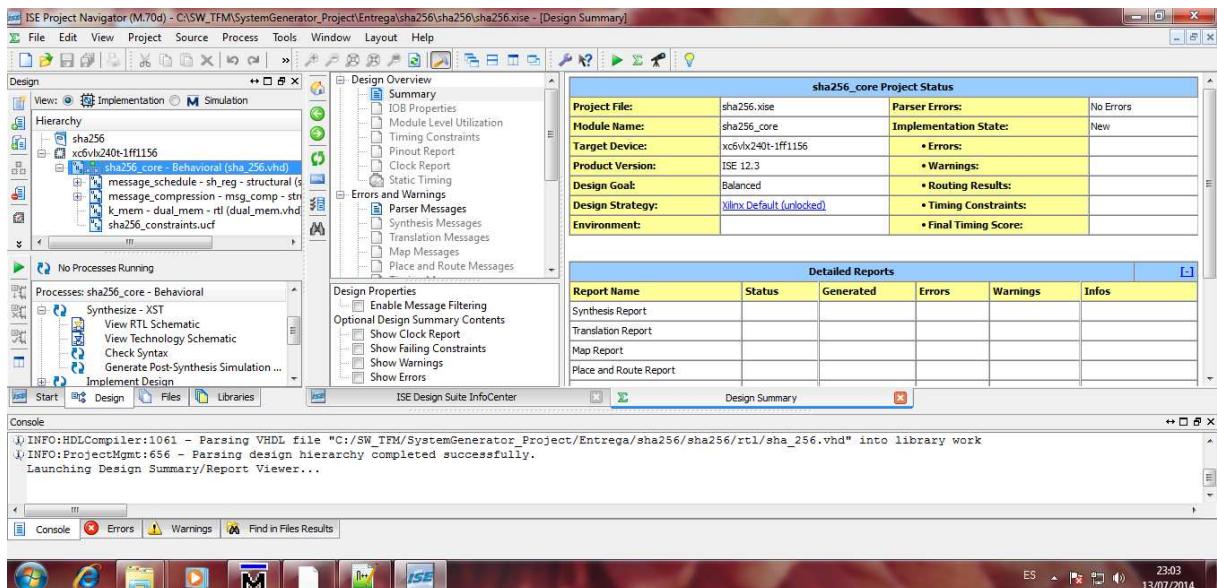

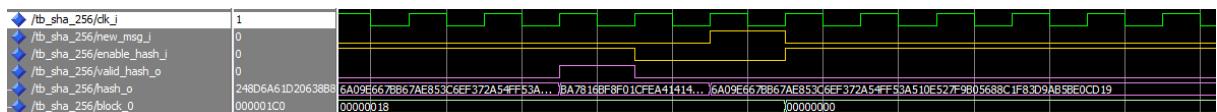

#### 5.3.2.1.1. Implementación

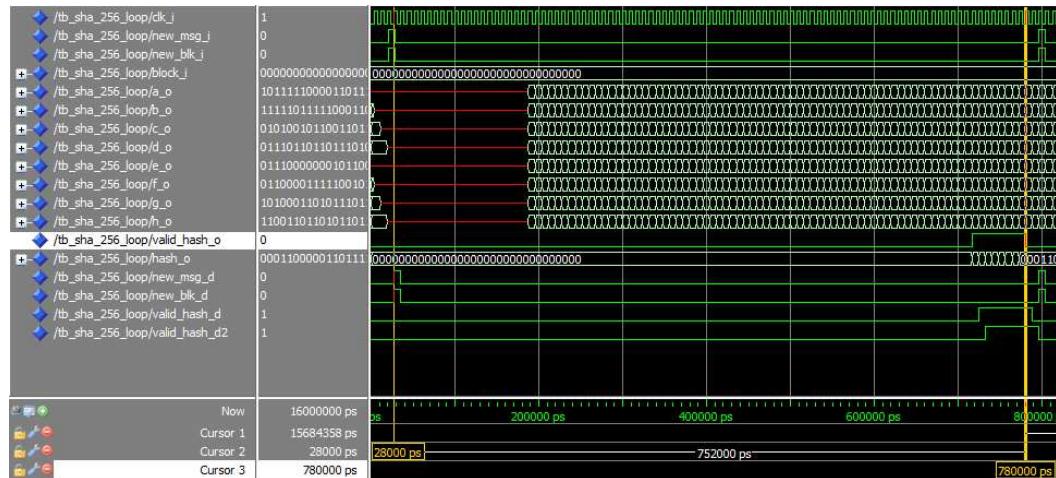

Para la implementación de este algoritmo se ha utilizado un componente en lenguaje VHDL denominado “sha256\_core”. Dicho componente tiene los siguientes puertos:

- clk\_i: Reloj del sistema.

- ce\_i: Enable del sistema. Requerido para generar un componente de tipo “black\_box” en System Generator aunque no se use interiormente.

- new\_msg\_i: Reset del componente. Debe mantenerse a ‘1’ durante un ciclo antes del comienzo de la transformación de un nuevo mensaje.

- new\_blk\_i: Indica que se desea trabajar con un nuevo bloque de 512 bits.

- block0-3\_i: Cuatro sub-bloques de 8 bits cada uno en los que se divide el bloque de 512 de bits que constituye el mensaje de entrada sobre el que aplicar la función

resumen. Por lo tanto, se requerirán 16 ciclos para capturar un bloque de 512 bits completo.

- a\_o,b\_o, c\_o,d\_o,e\_o, f\_o: Salidas que indican el valor contenido en los registros a-f y que servirán como señales de depuración en caso de algún fallo.

- valid\_hash\_o: Señal de validación de la salida “hash\_o”, indicando que está disponible el resumen del bloque de 512 bits de entrada.

- hash\_o: Resumen obtenido. Se trata de una señal 32bits, por lo que para proporcionar los 256bits que constituyen el resumen completo se requerirán 8 ciclos.

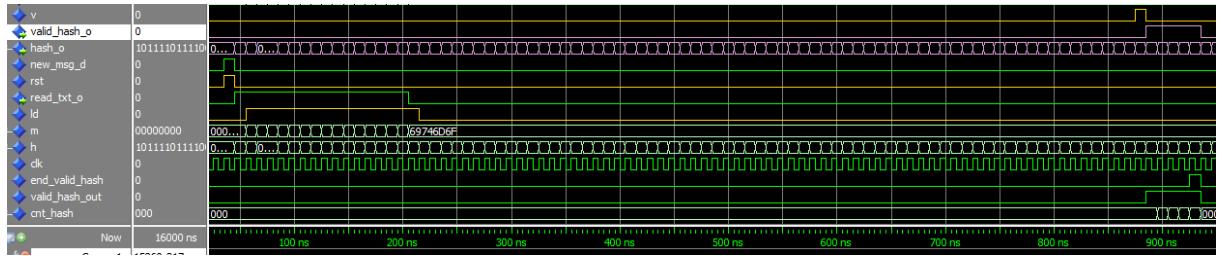

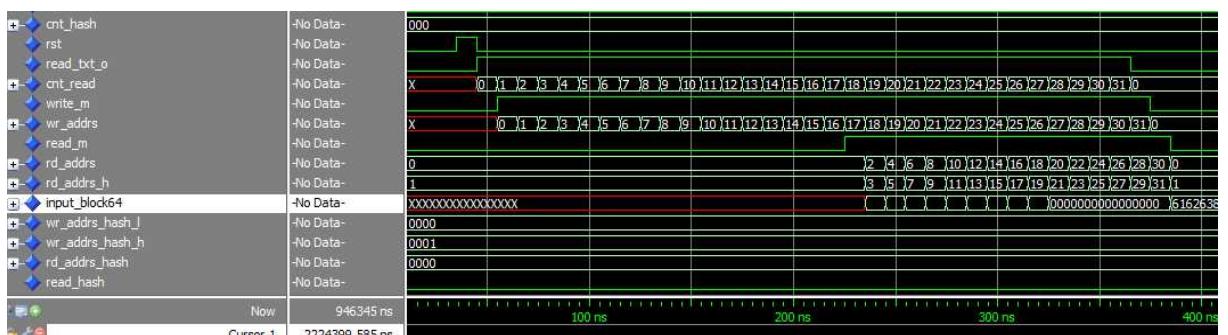

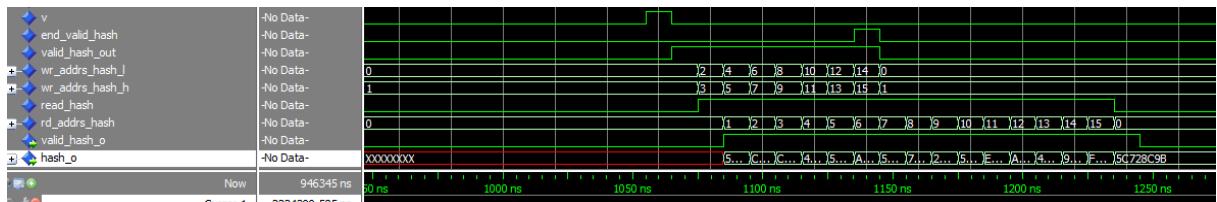

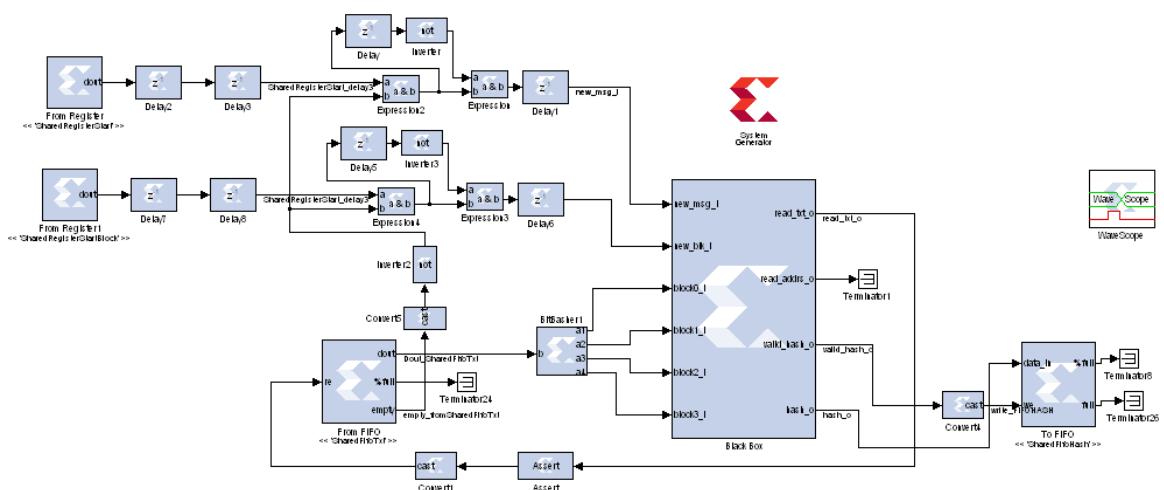

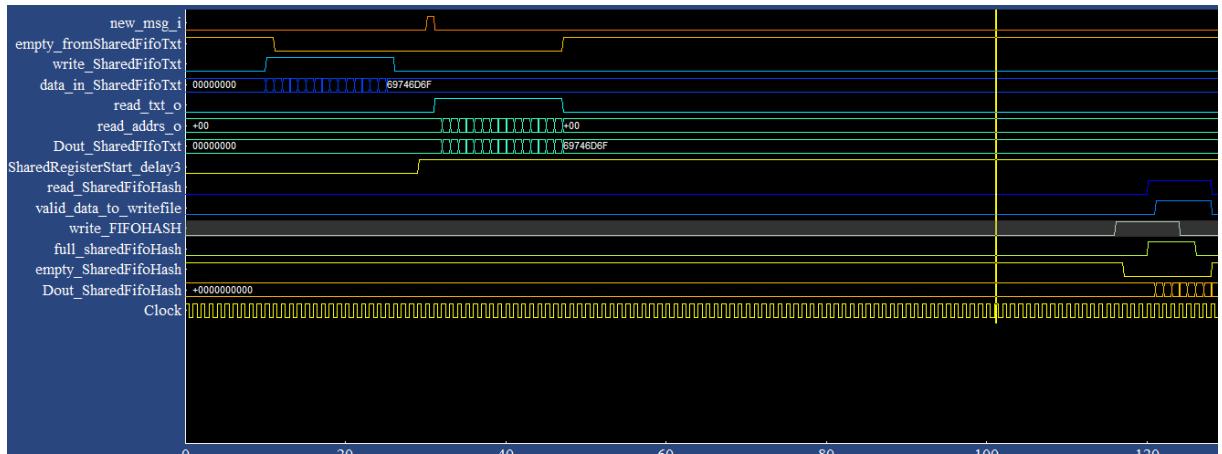

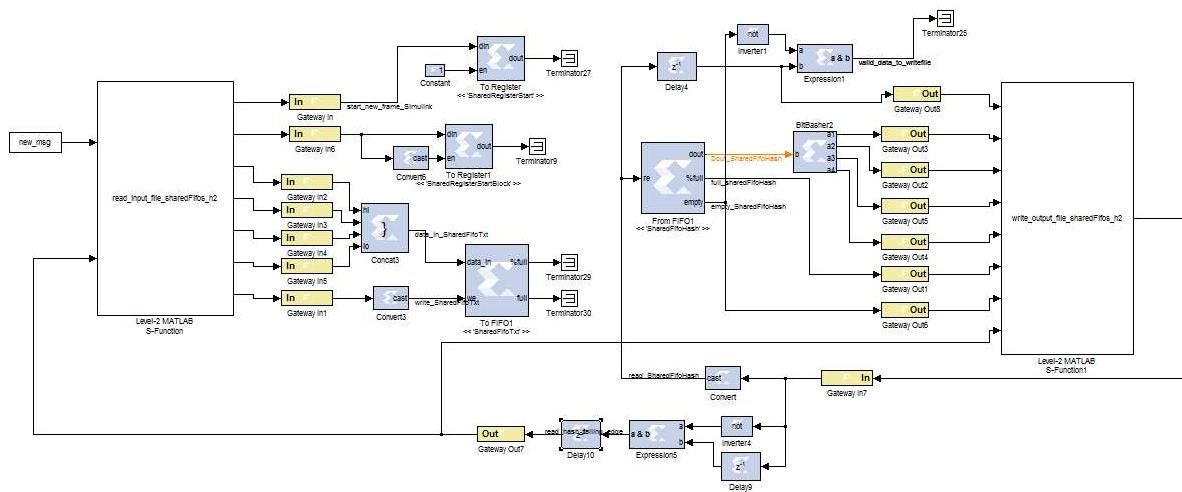

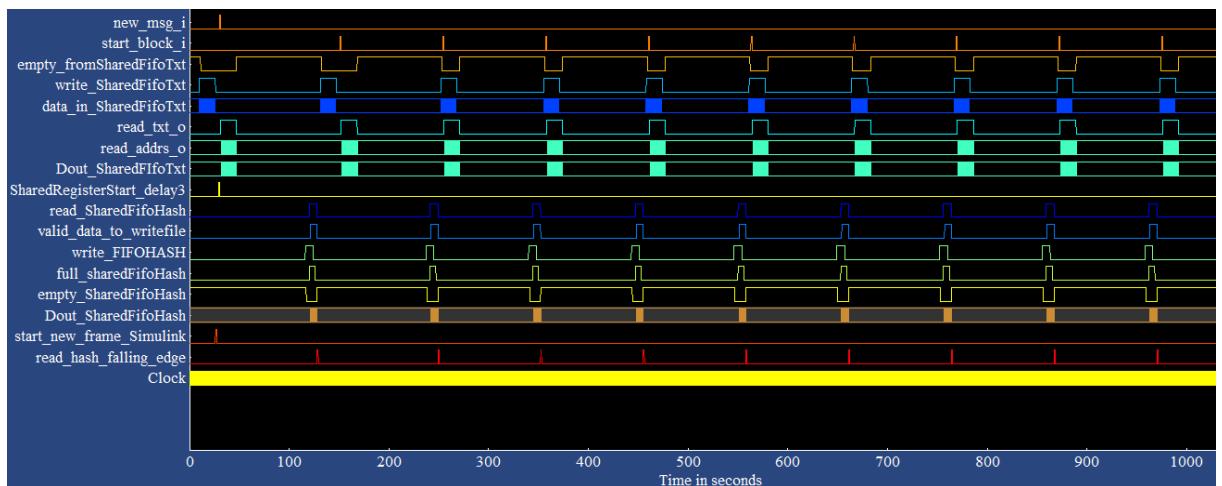

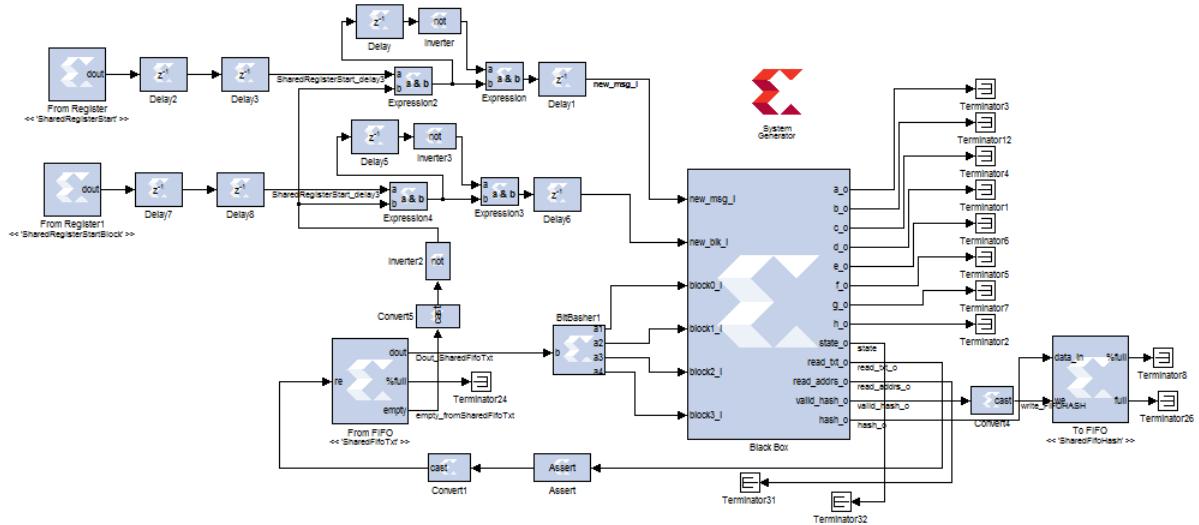

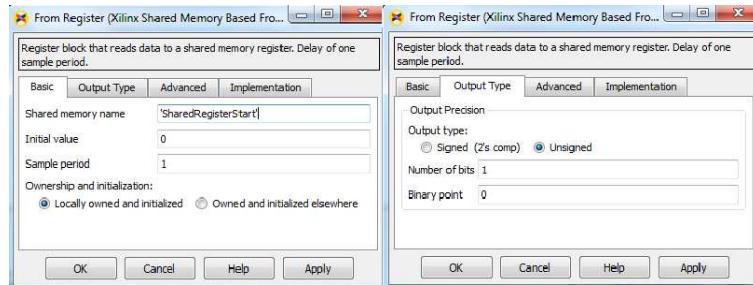

A grandes rasgos, la estructura de la implementación realizada de este algoritmo en la FPGA es la siguiente: