# **Hardware-in-the-Loop and Digital Control Techniques Applied to Single-Phase PFC Converters**

Paula Lamo <sup>1</sup><sup>(b)</sup>, Angel de Castro <sup>2</sup><sup>(b)</sup>, Alberto Sanchez <sup>2</sup><sup>(b)</sup>, Gustavo A. Ruiz <sup>3</sup>, Francisco J. Azcondo <sup>4</sup><sup>(b)</sup> and Alberto Pigazo <sup>3,\*</sup><sup>(b)</sup>

- <sup>1</sup> Escuela Superior de Ingeniería y Tecnología, Universidad Internacional de La Rioja, Avenida de la Paz, 137, La Rioja, 26006 Logroño, Spain; paula.lamo@unir.net

- <sup>2</sup> Dpto Tecnología Electrónica y de las Comunicaciones Ciudad Universitaria de Cantoblanco, Escuela Politécnica Superior, Universidad Autónoma de Madrid, 28049 Madrid, Spain; angel.decastro@uam.es (A.d.C.); alberto.sanchezgonzalez@uam.es (A.S.)

- <sup>3</sup> Dpto Ingeniería Informática y Electrónica, ETSIIyT, Universidad de Cantabria, Avd. Los Castros s/n, Cantabria, 39005 Santander, Spain; Gustavo.ruiz@unican.es

- <sup>4</sup> Dpto Tecnología Electrónica e Ingeniería de Sistemas y Automática, ETSIIyT, Universidad de Cantabria,

- Avd. Los Castros s/n, Cantabria, 39005 Santander, Spain; azcondof@unican.es

- Correspondence: pigazoa@unican.es

**Abstract:** Power electronic converters for power factor correction (PFC) play a key role in singlephase electrical power systems, ensuring that the line current waveform complies with the applicable standards and grid codes while regulating the DC voltage. Its verification implies significant complexity and cost, since it requires long simulations to verify its behavior, for around hundreds of milliseconds. The development and test of the controller include nominal, abnormal and fault conditions in which the equipment could be damaged. Hardware-in-the-loop (HIL) is a cost-effective technique that allows the power converter to be replaced by a real-time simulation model, avoiding building prototypes in the early stages for the development and validation of the controller. However, the performance-vs-cost trade-off associated with HIL techniques depends on the mathematical models used for replicating the power converter, the load and the electrical grid, as well as the hardware platform chosen to build it, e.g., microprocessor or FPGA, and the required number of channels and I/O types to test the system. This work reviews state-of-the-art HIL techniques and digital control techniques for single-phase PFC converters.

Keywords: power factor corrector; PFC; digital control; converter; Hardware-in-the-loop; HIL

# 1. Introduction

Active AC/DC converters ensure that the line current waveform complies with the applicable standards [1] and grid codes while regulating the DC voltage levels [2]. Searching for improvements in efficiency [3], power density and costs results in higher complexity control, involving multidisciplinary knowledge in design, development, testing and manufacturing stages [4].

Diverse alternatives to early prototyping have been used, such as mixed signal simulators [5], simulators with analog and mixed signal extensions [6], or using two simulators at the same time. However, these techniques have long simulation times and their development is complex [7]. Alternatively, Hardware-in-the-loop (HIL) is a technique for performing system-level testing of embedded systems in a comprehensive, cost-effective [8,9], and repeatable manner [10].

The power converter is mathematically modeled and then, a discrete model is implemented in a digital device, e.g., a microprocessor ( $\mu$ P), Field-Programmable Gate-Array (FPGA) or Application Specific Integrated Circuits (ASIC), which performs a real-time simulation of the power converter, the electrical grid and load. In these simulations, the

Citation: Lamo, P; de Castro, A.; Sanchez, A.; Ruiz, G.A.; Azcondo, F.J.; Pigazo, A. Hardware-in-the-Loop and Digital Control Techniques Applied to Single-Phase PFC Converters. *Electronics* 2021, *10*, 1563. https:// doi.org/10.3390/electronics10131563

Academic Editor: Khaled Ahmed

Received: 26 May 2021 Accepted: 25 June 2021 Published: 29 June 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). digital controller is evaluated as the hardware under test [11] and all the I/O channels, connecting the PFC model and the controller, are at low power levels.

This technique enables a real-time test of the actual controller to be carried out prior to building the plant, so that the simulated parts can be replaced by those already physically implemented as they become available; the test of the controller based on HIL avoids damaging the real plant in extreme situations and the reduction of the development cost, avoiding partial prototyping of the elements of the system and the cost of verification, as well as breakdowns in a real system [12–15]. Beyond that, different electrical and non-electrical systems are emulated on which a control action is validated through the HIL concept [16]. So this can be configured to emulate plants of different applications of electronic systems such as smart grids [17,18] and power converters [19–21], more specifically in PFCs [22,23].

Currently, the HIL implementation is realized with different platforms (e.g., µP, FPGA, ASIC) [24]. All these systems have common characteristics such as several processors working in parallel; a computer in which the offline model is prepared; input and output terminals interacting with external hardware; and a communication network that allows the exchange of data [25]. The use of FPGAs is preferred because they facilitate the computing parallelization; they allow smaller time-steps [26–28] and the possibility of optimizing the processing speed and area [29,30]. When using fixed point in the models or in the controllers, special attention must be paid to the resolution of the signals involved [7] to avoid the effects of limit cycle, stability problems and a high error in steady state.

HIL has been widely used in electrical power systems with grid-connected power converters [31,32], providing a reliable, economically effective and safe test-bench for development of power converters and their digital controls, within a more decentralized distribution power system scenario which imposes increasing efficiency and functionality requirements. The advantage that HIL brings to PFC controllers is centered on the simulation times that are handled in these systems. Since the PFCs work at the grid frequency, they require quite long simulations, of hundreds of milliseconds, to check dynamics and behaviors of the controller in the transients. PFCs and their controls play a key role in this scenario and are selected as the target for this review. The paper is organized as follows. Section 2 presents common technologies used in HIL. In Section 3, ways to model the converter and how to configure its arithmetic are shown. Section 4 discusses the types of digital control used in their stype of application, while, in Section 5, the HIL testing strategies that have been proposed in the literature are analyzed, finishing with conclusions.

#### 2. HIL Technology

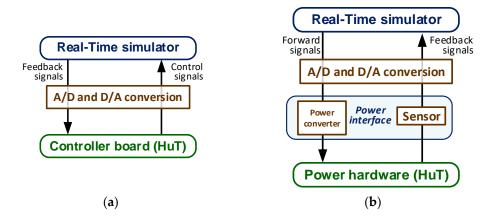

In a HIL simulation, the parts digitally simulated in real time totally replace the actual physical components of the system. The Hardware-under-Test (HuT) is tested by connecting it through input and output interfaces (e.g., filters or signal conditioners). It is also possible to execute limited control actions in real time (e.g., opening and closing of switches or disconnection of elements of the system). As is shown in Figure 1a, when the hardware model includes the actual control, it is called a Controller hardware-in-the-loop (CHIL). Since the energy system is virtually emulated, there is no real energy exchange in these systems. This is the paradigm commonly used in the power electronics industry to develop converter controllers that are tested using feedback signals from the controller and generating their own signals that are subsequently sent to the HIL. In the case in which the simulation involves energy transfer (Figure 1b), the system is called Power hardware-in-the-loop (PHIL) [33]. Here, part of the power system is internally emulated and the rest of the system is made up of a real hardware power device externally connected. In this case an energy source (power supply) or sink is needed.

HIL systems have the following characteristics in common [25]:

several processors working in parallel that jointly execute the simulation in realtime;

- ii. a computer in which the offline model is prepared in order to subsequently upload it to the destination platform and monitor the simulation results in real-time;

- iii. input and output terminals to interact with external hardware and

- iv. a communication system that allows the exchange of data between the different blocks that make up the system.

The choice of each element in a smart grid is evaluated in [33] relating them to bandwidth, stability, model accuracy, limitations of smaller time steps, performance and capability limits on actuators and sensors of the interfaces, nonavailability of assessment methodologies, cost and optimization.

Figure 1. Basic HIL simulation: (a) CHIL and (b) PHIL.

The first HILs were based on the use of computers to carry out the simulations [34]. Its historical and technical evolution in the last 50 years is analyzed in depth in [35].

Despite the above, the use of FPGAs for modeling this type of system makes it necessary to define the arithmetic type used. Determining factors of the system depend on this decision, such as the simulation step, the hardware resources used in the FPGA and the simplicity of design. To simplify this task, high-level tools are available, such as MATLAB or PSIM models, which perform automatic translations into HDL code [34]. In [36], an in-depth analysis of the different software and tools which can be used for the implementation of code in FPGAs in industrial applications, such as those discussed in this work, is made. Another possibility is the use of commercial hardware tools, such as spHIL [37], Typhoon HIL, dSPACE [38], Opal-RT or RTDS [39], which facilitate the design of the models through graphical interfaces and preconfigured models. In [40], a comparison of the different commercial simulators available is included. These FPGA-based systems use complex models defined by the user without the need for optimization knowledge with small integration steps (around 1 us) and PWM input reads of around 10-20 ns. However, they are practically mandatory in complex systems such as [41], where the mitigation of grid harmonics in photovoltaic inverters is studied, or [42], where a fast charger for electric vehicles is tested. In these cases, although the commercial HIL facilitates the realization of the model, the results obtained in terms of consumed resources or integration step are not always optimized [34]. Some companies also offer customized HIL, like Power Smart Control [43].

## Commercial HIL

Recently commercial tools have emerged capable of carrying out HIL simulations. HIL is described through schematics, such as electrical simulators. The tool can transform the design of the user into an executable model on a hardware platform from the same manufacturer. These platforms are based on microprocessors, FPGAs or a mixed architecture. Although the equipment runs on an FPGA, it uses an embedded microprocessor to implement the communications and SCADA-type functionalities. In this sense, Typhoon offers its own integrated development environment (IDE) and schematic editor. Other manufacturers, such as SpeeGoat, Opal-RT [44] or dSPACE [45], use MATLAB/Simulink as their editor. The user uses the Simulink libraries to design the model and, later, that tool of the manufacturer compiles the model that will run in their software.

On the other hand, there are tools that, without being focused on performing HIL, allow some models to be executed in various formats on FPGA-based hardware platforms. NI LabVIEW is a tool based on the graphical programming paradigm called G used by all kinds of instrumentation and control applications and includes SCADA functionality in the tool. NI manufactures its own hardware platforms to augment the technical capabilities of LabVIEW, from data acquisition cards to hardware acceleration platforms. The LabVIEW FPGA functionality allows downloading models or part of them to FPGAs that can be used to create HIL graphical models with the equations of the converter (in other words, it is necessary to write the equations manually) [46]. However, in comparison with the VHDL language, there are limitations, such as time resolution [47]. Another possibility is to use the Real-Time toolbox of MATLAB/Simulink to download models on FPGAs. This option is limited by the number of elements that the toolbox library has but, in return, it allows designs through its schematics or the modeling of the equations in Simulink. In this sense, the company SpeedGoat offers itself as an official partner for HIL from MATLAB/Simulink for its schematics [48].

In [49], a review is made of the main commercial tools in HIL without acquiring a high-cost HIL machine, mainly through evaluation tools. The study analyzes the theoretical characteristics of the tools offered by Typhoon, LabVIEW (comparing "Control Design & Simulation" and "LabVIEW FPGA" tools) and MATLAB/Simulink (comparing "Real Time Desktop" and "Real Time" tools), by observing their specifications and limitations. In the study, Typhoon is shown as the most powerful tool that includes more capabilities from the hardware point of view and its modeling and simulation are more intuitive. LabVIEW offers greater model customization capabilities. While MATLAB has the disadvantage that its "Real Time Desktop" tool simulates inside the processor of the computer that runs it, it does not show use/performance results in specific hardware and "Real Time" needs a physical hardware device to be able to simulate. Table 1 gives a summary of the main characteristics analyzed in [49].

| Table 1. Comparative analysis of Typhoon, LabVIEW ("Control Design & Simulation" and "LabVIEW FPGA") and             |

|----------------------------------------------------------------------------------------------------------------------|

| MATLAB/Simulink ("Real Time Desktop" and "Real Time") tools, according to [49]. (Reprinted with permission from ref. |

| [49]).                                                                                                               |

|                     |                                                                                                                                                           | LabVIEW                                                                                                                                                                                                                                                          |                                                                                                                                     | Simulink                                                                                                                                                                                     |           |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                     | Typhoon HIL                                                                                                                                               | Control Design &<br>Simulation                                                                                                                                                                                                                                   | LabVIEW FPGA                                                                                                                        | Real Time<br>Desktop                                                                                                                                                                         | Real Time |

| Solvers             | Exact<br>Trapezoidal<br>Euler                                                                                                                             | Runge-Kutta 1 (Euler), 2, 3, 4,<br>23 (variable), 45 (variable)<br>BDF (variable)<br>Adams-Moulton (variable)<br>Rosenbrock (variable)<br>Discrete States Only<br>SDIRK4 (variable)<br>Radau 5, 9, 13 (Variable Order)<br>(variable)<br>Gear's Method (variable) | The solver used is<br>defined in the<br>logical and<br>mathematical<br>model chosen<br>during the<br>realization of each<br>design. | Discrete (no continuous states)<br>Ode8 (Dormand-Prince)<br>Ode5 (Dormand-Prince)<br>Ode4 (Runge-Kutta)<br>Ode3 (Bogacki-Shampirne)<br>Ode2 (Heun)<br>Ode1 (Euler)<br>Ode14x (extrapolation) |           |

| Data<br>acquisition | Allows data export<br>in various formats<br>during simulation<br>in HIL SCADA<br>(CSV, HDF5, HDF5,<br>MAT, TDMS)<br>HIL402 has built-in<br>oscilloscopes. | Allows to export results<br>directly in Excel or clipboard.                                                                                                                                                                                                      | Need other<br>hardware to<br>display the<br>simulated signals.                                                                      | The data of the different signal can be saved and/or plotted.                                                                                                                                |           |

|                                               |                                                                                                                                   | LabVIEW                                                                                                                                                                                                                                   | Simulink                                                                                                 |                                                                                                                                                                                                 |                                                                                                                   |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                               | Typhoon HIL                                                                                                                       | Control Design &<br>Simulation                                                                                                                                                                                                            | LabVIEW FPGA                                                                                             | Real Time<br>Desktop                                                                                                                                                                            | Real Time                                                                                                         |

| Clock<br>frequency                            | With the HIL402<br>hardware virtual<br>machine: 50 MHz                                                                            | Simulating loops of "Control<br>Design & Simulation" at<br>different frequencies<br>(1 kHz, 1 MHz and in<br>between).<br>Maximum frequency in real<br>time (RT): 1 kHz                                                                    | MyRIO-1900<br>Maximum Clock<br>Rate with<br>Zynq-7000 FPGA:<br>40 MHz                                    | Maximum<br>possible<br>frequency in real<br>time (RT) in<br>normal mode:<br>1 kHz<br>In external mode:<br>20 kHz                                                                                | Depends on<br>the hardware<br>to be used.                                                                         |

| Switching<br>frequency                        | With the HIL402<br>hardware virtual<br>machine: 200 kHz                                                                           | The switching frequency shall<br>not be higher than the clock: 1<br>kHz                                                                                                                                                                   | Depends on the<br>hardware to be<br>used, but never<br>higher than the<br>clock frequency: 40<br>MHz     | In normal mode:<br>1 kHz<br>In external mode<br>it is a function of<br>the selected<br>Duty:<br>$f_{SW} = f_{CLK} \times$<br>Duty                                                               | Depends on<br>the hardware<br>to be used.                                                                         |

| Minimum<br>simulation<br>step                 | With HIL402<br>hardware: 500 ns                                                                                                   | 1 ms                                                                                                                                                                                                                                      | Depends on the<br>model with a<br>theoretical<br>minimum of 25 ns<br>(40 MHz clock).                     | In normal mode:<br>1 ms<br>In external mode:<br>50 μs                                                                                                                                           |                                                                                                                   |

| Real Time<br>simulation                       | Works in Real Time<br>on the HIL402<br>virtual machine.                                                                           | Simulation at various<br>frequencies (on a PC with 1<br>kHz clocks or derivatives and<br>with a 1 MHz NI HW or<br>similar), but to be a real<br>real-time simulation, only 1<br>kHz is allowed with steps or<br>steps of periods of 1 ms. | Realtime on<br>specified NI<br>hardware:<br>myRIO-1900.                                                  | In real time at the specified frequencies using the computer's own processor. In external mode the circuit model is converted to a $C/C$ ++ model which implies a higher frequency to simulate. | In real time<br>on the<br>hardware<br>connected to<br>the<br>equipment<br>and linked to<br>the designed<br>model. |

| Resource<br>utiliza-<br>tion/occupied<br>area | Shows summary of<br>HW resources,<br>memory and SW<br>size. Use more<br>high-level built-in<br>resources.                         | Does not show details.                                                                                                                                                                                                                    | During the board<br>design, the report<br>shows low-level<br>components (slices,<br>LUTs, DSPs ).        | Allows analysis of the use of resources.                                                                                                                                                        |                                                                                                                   |

| Licensing                                     | Free "Typhoon HIL<br>Control Center"<br>software<br>download and<br>registration.<br>Virtual machine<br>with a 1-year<br>license. | LabView 2019 and Multisim<br>14.2 require a license or the<br>45-day free trial.                                                                                                                                                          | Need the NI<br>myRIO module<br>included with the<br>hardware, and the<br>LabVIEW FPGA<br>payment module. | Simulink Real Time Desktop (not<br>Simulink Real Time) requires<br>license.<br>To make the circuit designs, you<br>need a paid "Simscape Electrical"<br>or a 1-month free trial version.        |                                                                                                                   |

| Type of simulation                            | On-line                                                                                                                           | Off-line                                                                                                                                                                                                                                  | On-line                                                                                                  | Off-line                                                                                                                                                                                        | On-line                                                                                                           |

Table 1. Cont.

### 3. Converter Modeling

HIL implementations rely on precise mathematical models to replicate the power converters, along with hardware platforms, in order to be efficient in real time applications. In this section, proposed mathematical approaches and arithmetic used in the converter operation as well as digital hardware implementations of the HIL are described.

#### 3.1. Mathematical Model

Different mathematical models can be used to describe the behavior of an electronic converter. Although some HIL systems implements an average model of the converter [50,51], the majority of HIL systems use switched models [52]. This is because the switched models are more realistic, as they directly calculate the evolution of every state variable in a small simulation step, being able to reproduce the high frequency events such as the switching noise. Therefore, they are more useful for closed-loop debugging.

The average linearized small signal model [53] consists in linearizing of the system around an operation point. The advantage of this approach is the easy understanding of the system through circuit-based models. But the averaged linear time invariant (LTI) approximation is not accurate enough for PFC applications [54]. As an example, in [22], the converter is modeled via the averaged switch approach because the modeled equations can be solved fast enough within the chosen small time step.

The whole power converter can be modeled with a set of differential equations that, after discretization, result in a state space (SS) model which must be calculated using the values of the state variables in every simulation step [34].

The average model Euler-Lagrange (EL) is used for obtaining the average model, and its converters serve as a basis for obtaining the nonlinear models. In [55], a Lagrangian approach is used to obtain the average model of a Boost converter and is proposed, which recovers, under extreme duty ratio saturation conditions, the individual EL formulations of the intervening topologies of the circuit. In [56], the average Boost converter circuit is also written by EL equations.

The Hamiltonian modeling encompasses the Lagrangian and represents the systems as interconnection ports, where the product of the port variables is the power, that is the rate of change of energy [57]. The state variables are those related to energy store elements, such as capacitors and inductors. Despite having specific mathematical and physical interpretations, Port—Controlled Hamiltonian (PCH) model can be obtained by EL model and both are mathematically similar to the models described in state space. An example of application of the Euler-Lagrange, state space and PCH models is shown in [58].

In [23], the model of the PFC stage is reached by dividing the circuit into a linear part, using a state space representation based on the Padé approximant and a nonlinear part, given by a switch state dependent feedback.

Table 2 summarizes the main specifications of the proposed HILs which use different mathematical approaches to comply with reliable models of converters. Moreover, contrast experiments to validate the suitability of these models and their implementation in different platforms are also highlighted.

| Proposal | Mathematical<br>Model                   | Converter                | Experimental<br>Verification         | Platform |

|----------|-----------------------------------------|--------------------------|--------------------------------------|----------|

| [47]     | LTI + State Space                       | LLC resonant             | PSIM                                 | FPGA     |

| [24]     | Average switch<br>approach              | AC-DC PFC                | MATLAB/Simulink<br>(CHIL simulation) | РС       |

| [34]     | State space/Euler<br>Lagrange           | Buck                     | LT3430-1/LTC3892-<br>1/MAX1685       | FPGA     |

| [50]     | Euler-Lagrange                          | Boost, Buck and<br>SEPIC | MATLAB/Simulink<br>(Real plant)      | DSP      |

| [25]     | Padé approximation<br>with oversampling | Rectifier PFC            | MATLAB/Simulation<br>(Real plant)    | FPGA     |

Table 2. Specifications of the proposed HILs.

## 3.2. Arithmetical Possibilities

The election of the mathematical model must be associated with the choice of the arithmetic to be used in the HIL model. The latter is responsible for defining key HIL parameters, such as its size, e.g., memory or area requirements, or the minimum simulation step, i.e., time resolution. The choice of the arithmetic depends on the target used for the implementation ( $\mu$ P, FPGA, ...) but also the abstraction level and development tools due to the language used must be considered (VHDL, C, Verilog, ...). For example, in [34], the following VHDL classification is presented:

- 1. Real Arithmetic: this is the standard numeric type that uses double-precision floatingpoint format. It cannot be synthesized, but it is useful to create a first approximation.

- 2. Float Arithmetic: this is a synthesizable floating-point arithmetic. It has the versatility of floating point, but it needs many hardware resources.

- 3. Fixed Arithmetic: this is a fixed-point arithmetic. The designer must decide the number of bits to the integer and the fractional parts of every variable, and it needs much more design effort.

Floating point arithmetic is easier to use and translating equations from the mathematical model to code is straightforward in most cases. An example of this application is shown in [59] where the DCDC converter was described with single precision floating point arithmetic with a state-space approach and two states. In cases where the simulation step is critical, the fixed point is more interesting. In [7], a power converter is modeled using different arithmetic and it is evidenced that the use of a fixed point increases the processing speed and decreases the number of hardware resources used. This same result is shown in Table 3, where an addition and subtraction operation are synthesized using two numbers in fixed point and in floating point using xc7a100t-csg324-1 FPGA in Xilinx Vivado, where the timing is nine times faster in the case of 32-bits integer than with 32-bit floating point [60]. On the other hand, some platforms allow configuring the resources consumed in an operation to adapt to the needs of the system. Table 4 shows an example of how it is possible to define different resource settings and delay times in the same operation using a multiplication of two floating point numbers employing xc7a100t-csg324-1 FPGA in Xilinx Vivado.

Although synthesis tools have evolved enormously in recent years and these differences have been diminishing with new tools, these differences still exist. However, it cannot be the only element to consider when choosing arithmetic since using fixed point in complex converter models can involve a significant design effort that may not be attractive [34]. With the use of fixed point, it is necessary to define in each stage the location of the point that will be fixed according to the range of values that the variable takes and it will be necessary to modify it with each reconfiguration proposed.

| Operation                     | DSP48E | LUT | Timing    |

|-------------------------------|--------|-----|-----------|

| float32 $	imes$ float32       | 3      | 135 | 52.435 ns |

| float32 + float32             | 2      | 195 | 88.970 ns |

| $int32 \times int32$          | 4      | 231 | 19.315 ns |

| <i>int</i> 32 + <i>int</i> 32 | 0      | 186 | 4.658 ns  |

**Table 3.** Summary of the hardware resources and timing in an FPGA by performing addition and multiplication operations with two 32-bit numbers using fixed point and floating point (int32 and float32, respectively).

DSP48E and LUT are digital signal processing logic and Look Up Table elements, respectively.

**Table 4.** Summary of the hardware resources and timing in an FPGA by performing multiplication operations with two floating point numbers.

| Operation                 | DSP48E | LUT | Timing    |

|---------------------------|--------|-----|-----------|

| float $32 \times float32$ | 0      | 675 | 78.780 ns |

| $float32 \times float32$  | 1      | 267 | 67.505 ns |

| $float32 \times float32$  | 2      | 122 | 54.690 ns |

| $float32 \times float32$  | 3      | 135 | 52.435 ns |

### 4. Test

Testing controllers for power converters using HIL are gaining acceptance. Recent proposals include the following representative examples:

- Statistical tests [61], such as the Monte Carlo method, that require multiple iterations to simulate failure cases.

- Low-cost multi-solver real-time simulation environment [62], namely the real-time extension of the virtual test bed (VTB-RT). In this proposal, for a given hardware platform, the minimum time resolution is limited and only a limited bandwidth of the system under test can be used. So it is necessary to pay attention to the compromise between the VTB-RT platform cost and the bandwidth of the system under test.

- Reconfigurable HIL based on a top-down design flow [63] analyzed through a faulttolerant shunt active power filter application. In [64], it is also shown how HIL devices are used to assist in the design, optimization and quality assurance of controllers from the early design stage all the way to the type testing and release testing stage.

- HIL for the validation, in the time and frequency domains, of the input and output impedances of converters achieving ultra-low latency in real time [65]. This work also shows a comparison between real-time emulation and a reference hardware design under steady-state and transient conditions.

### 5. Digital Control

The difference between the response obtained when the controller interacts with the HIL and the actual converter is caused by the latency between the signals sent by the con-troller and the output of the HIL. The total latency must be kept to a minimum by using a very small-time interval during the simulation [66].

Generally, the control in PFC is done with two loops: an internal and fast current loop to achieve near unity power factor, and an external and slow voltage loop to stabilize the output voltage. In this case, usually three variables are necessary: input and output voltage ( $v_{in}$  and  $v_{out}$ , respectively), and input current ( $i_{in}$ ), although there are other proposals in the literature, as in [67–69], that eliminate the need to use the current sensor.

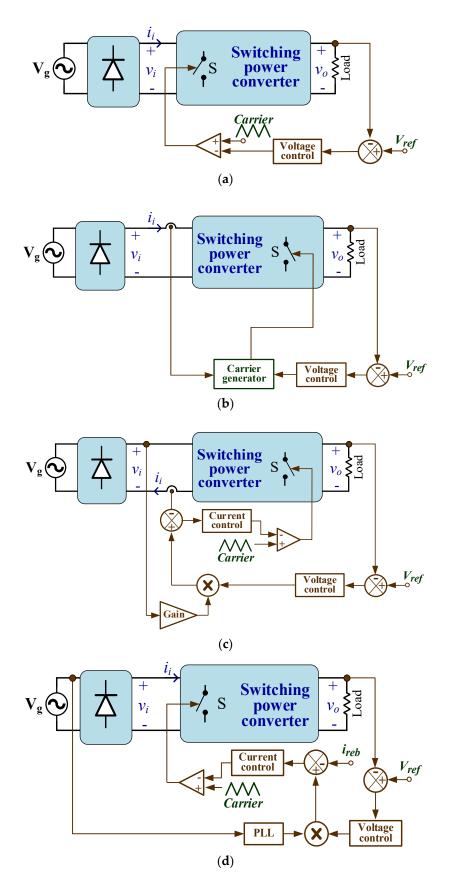

According to [70], current control techniques classify the digital control of the PFCs into four groups (Figure 2):

- 1. Group I: Operation in discontinuous conduction mode (DCM) or the boundary condition between the continuous conduction mode (CCM) and DCM (Figure 2a).

- 2. Group II: Non-linear carrier (NLC) control of the line current, where the switching instants are identified by the comparison of the current with a carrier signal, hysteresis

band or a sliding surface that imposes the proportionality between the peak, valley, or average current and the input voltage in each switching period (Figure 2b).

- 3. Group III: Linear control of the average current. Noise immunity improves compared to the NLC technique at the expense of reducing the bandwidth of the current control (Figure 2c).

- 4. Group IV: Phasor-based control. The input voltage is assumed to be sinusoidal, so the modulation function that imposes the line current must be sinusoidal (Figure 2d).

As an example of Group I, in [71], the operation characteristics, the modeling and the control system of the DC-DC SEPIC PFC converter in CCM and DCM are presented. The authors compare two different controllers and finally, they suggest a new nonlinear controller called Adaptive Passivity-Based Feedback Linearization Control.

The non-linear control, Group II, is the best adapted to the different operating points of a non-linear and time-varying system such as the converter. In its original version it is implemented with a simple comparator (in its average version, the complexity does not increase substantially). These attributes make it a very interesting option to leverage the digital circuit capabilities, improving the noise immunity and including predictive algorithms. One example of this is [56], where the non-linear control of a boost converter PFC and SEPIC converter is tested; while, in [72], nonlinear control techniques applied to static power converters are implemented and compared in HIL: State Feedback Linearization (SFL), passivity Based Control (PBC), and Interconnection and Damping Assignment Passivity Based Control (IDA-PBC). Here, each model is associated with a control technique. The EL model is the base model for the others. The Euler-Lagrange model is associated with PBC control equations, SFL control uses the model description in state space (SS), and the IDA-PBC control requires the PCH system.

Group III controls present the following advantages:

- 1. Its bandwidth of the current acquisition stage is smaller than in the non-linear version.

- 2. In bidirectional PFCs, the non-linear control may exhibit non-stable operating conditions.

It has better immunity to high frequency noise due to its lower bandwidth (both sensor and control loop), as well as acquisition techniques (synchronization between acquisition and switching).

An example of the Group IV technique, based on the introduction of sinusoidal input voltage, gaining immunity to grid disturbances, is shown in [73] where a traditional linear control with two loops is proposed for a bridgeless SEPIC PFC converter. In [74], the proposed control is based on a multi-thread software structure where time critical tasks are performed in a fast interrupt service routine, repeated every switching cycle in a totem pole PFC. Appropriate control measures are employed to address current spikes during zero crossings and AC voltage drop handling issues.

**Figure 2.** Types of current control techniques in PFCs. (**a**) Group I, (**b**) Group II, (**c**) Group III and (**d**) Group IV.

In [75], the contributions of FPGAs to the control of industrial systems, including power electronic converters, are presented, establishing three main design rules that focus on the algorithm refinement, the modularity, and the systematic search for the best compromise between the control performance and the architectural constraints. Another common option is to find the use of FPGAs together with processors [35] where the FPGA carries out sampling and conditioning tasks of input and output signals in parallel to the processor. Examples of this type of system are dSPACE and Opal-RT [35].

#### PWM

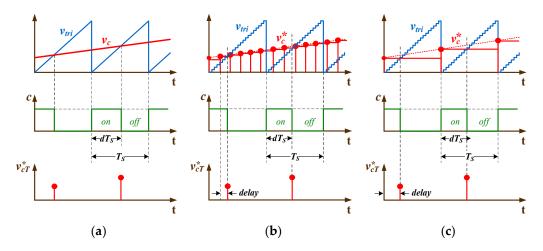

The pulse width modulator (PWM) is the block that samples the output signal of the controller. In a first approximation to this block (Figure 3a), which corresponds to natural sampling, the generation of PWM comes from the comparison of the modulating signals, resulting from the control action,  $v_c$ , and a linear function, the carrier, in the period of switching. When a digital controller generates the control signal there is a double digitization (Figure 3b) where the signal  $v_c^*$  is the output signal of the digital controller, whose update period depends on the clock of the digital circuit, and  $v_{cT}^*$ , which is the control signal sampled by the PWM block. If uniform sampling is adopted, the value of  $v_c^*$  is taken at the beginning of each switching period to obtain the PWM signal (Figure 3c), avoiding the occurrence of a vertical crossing [76].

**Figure 3.** PWM modulator with trailing edge sawtooth carrier signal. (**a**) Natural sampling, (**b**) double sampling of the control signal, and (**c**) sampling of the control signal at the beginning of each switching period.

This comparison of the two signals generates a logic 0 and 1 output signal, indicating the off and on state of the switch respectively. The resolution of the PWM depends on the number of clock cycles in the switching period and the type of carrier. In [77], how to increase the resolution of the PWM block is presented, oriented to prevent one of the limit cycle conditions.

The literature shows examples of PWM that use from a minimum of 20 samples per PWM period [59] to hundreds [64] or even thousands [78]. In addition, it is possible to synthesize different types of digital pulse width modulators, depending on the relationship between the sampling frequency and the switching frequency and different carrier waveforms [79], and use numerically different PWM sampling and simulation steps (for example, in the commercial tool Typhoon HIL602 the PWM sampling step is 20 ns, and the simulation step is reduced to 500 ns [80]).

Control and carrier signals are both the elements under the test carried out by interacting with the HIL and are finally implemented in the real system. Their implementation is therefore not a model, but the actual design. It is common to adopt the switching period as the sampling period for the controller, which introduces a known error and time delay in comparison with the analog counterpart, so design constraints to limit those effects are introduced. However, the carrier signal of the PWM block or the NLC has the largest resolution, allowed by the digital implementation of the controller in the actual converter, because this resolution defines the achievable step change of the power variables, i.e., current and voltage. On the other hand, the higher the time resolution of the platform that allocates the HIL, the closer are the results achieved to the actual converter response. FP-GAs are preferred to develop HIL projects because of their capability of defining concurrent digital blocks, and thus make the most of the clock time resolution.

## 6. Conclusions

This manuscript provides an overview of HIL and digital control techniques applicable to single-phase PFCs. Initial verification stages in early PFC prototypes are avoided through HIL, which reduces the product time to market and the development costs.

After introducing HIL and approaches used for PFC design and validation, an overview of the available customized and more general tools is also given. From a user perspective, the main differences rely on the maximum accuracy and resolution achieved in each case and, generally speaking, customized tools result in better resolutions by selecting the most suitable target, mathematical model and solver for each application. However, more generalist tools provide a better integration with other tools required during the design, or the final verification stages. The modelisation of the power converter is also a key point to achieve the required accuracy and time resolution. State space, average and switch, and Euler-Lagrange approaches are commonly used in HILs for PFCs. However, not only is the mathematical model relevant, but also the selected target for the HIL. The most commonly used target for HIL in PFCs is FPGAs, which allows the best time resolution among the available targets.

The choice of technology and model to use for the development of a HIL depends on the type of application and the available budget. To make a low-cost version, the designer can use tools such as spHIL, which include a very intuitive graphical interface to configure the pre-designed models and use an inexpensive FPGA (over 100 euros). However, if it is necessary to design an ad-hoc model not included in a commercial product, an economical solution is to design a custom model and implement it in an FPGA using VHDL language, or use a NI myRIO device and design the HIL model using a graphical language in LabView. Following Table 1, the latter limits the HIL capabilities but gains in flexibility. When requiring higher performance, it is necessary to use a specific commercial system for HIL, such as Typhoon HIL, dSpace or Opal-RT. These systems are scalable and the design procedure of the HIL is carried out through the schematic of the power stage in a very patterned way. However, the cost of this type of system is high (over several thousand euros).

The digital controller receives inputs from the HIL and generates the switch-gate signals. This implies that the HIL complexity, hardware resources in terms of both A/D and D/A interfaces and processing capability should be adapted to the type of used controller. Moreover, certain control techniques, such as current rebuilding, involve a high time resolution, which also affects the decision about the mathematical model, solver and selected target for HIL.

All in all, mathematical models, solvers, targets and digital controllers must be balanced to speed up the verification stage of the power converter and its controller. These proposals can be developed through more general high-level techniques, which are fast and consume large hardware resources, or through ad hoc designs in which the designer must specify the mathematical model, arithmetic and technology to be used based on their needs.

**Author Contributions:** The paper was written by P.L. and was revised by the rest of the authors (A.d.C., A.S., G.A.R., F.J.A. and A.P.). A.d.C. and A.S. contributed with HIL Technology. G.A.R. contributed with mathematical models and the bibliographic search. F.J.A. and A.P. contributed with Digital Control. All the authors were involved in preparing the final version of this manuscript. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Spanish Ministry of Science and Innovation under Project RTI2018-095138-B-C31 PEGIA—Power Electronics for the Grid and Industry Applications.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- Commission, I.E. Electromagnetic Compatibility EMC—Part 3-2: Limits for Harmonic Current Emissions (Equipment Input Current ≤ 16 A per Phase); 2021; Volume 2. Available online: https://infostore.saiglobal.com/preview/422560892461.pdf?sku= 1144674\_SAIG\_NSAI\_NSAI\_2712803 (accessed on 24 June 2021).

- Nguyen, H.V.; Lee, D. Reducing the Dc-Link Capacitance: A Bridgeless PFC Boost Rectifier That Reduces the Second-Order Power Ripple at the Dc Output. *IEEE Ind. Appl. Mag.* 2018, 24, 23–34. [CrossRef]

- 3. Potera, R.R.; Han, T.J. Silicon Carbide Diodes in Power-Factor Correction Circuits: Device and Circuit Design Aspects. *IEEE Power Electron. Mag.* **2019**, *6*, 34–39. [CrossRef]

- Yan, S.; Tan, S.; Lee, C.; Chaudhuri, B.; Hui, S.Y.R. Use of Smart Loads for Power Quality Improvement. *IEEE J. Emerging Sel. Top.* Power Electron. 2017, 5, 504–512. [CrossRef]

- 5. Ghosh, S.; Giambiasi, N. Modeling and Simulation of Mixed-Signal Electronic Designs—Enabling Analog and Discrete Subsystems to Be Represented Uniformly within a Single Framework. *IEEE Circuits Devices Mag.* 2006, 22, 47–52. [CrossRef]

- Pecheux, F.; Lallement, C.; Vachoux, A. VHDL-AMS and Verilog-AMS as Alternative Hardware Description Languages for Efficient Modeling of Multidiscipline Systems. *IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.* 2005, 24, 204–225. [CrossRef]

- Sanchez, A.; de Castro, A.; Garrido, J. A Comparison of Simulation and Hardware-in-the- Loop Alternatives for Digital Control of Power Converters. *IEEE Trans. Ind. Inform.* 2012, *8*, 491–500. [CrossRef]

- 8. Larruscain, G.; Tapia, G.; Susperregui, A.; Martinez, M.I. Student-Tailored Final Year Project on Microcontroller-Based Hardwarein-the-Loop Speed Control of a Wind Generator. *Int. J. Electr. Eng. Educ.* 2018, *55*, 213–233. [CrossRef]

- 9. Ahmad, Z.; Torres, J.R.; Veera Kumar, N.; Rakhshani, E.; Palensky, P.; van der Meijden, M. A Power Hardware-in-the-Loop Based Method for FAPR Compliance Testing of the Wind Turbine Converters Control. *Energies* **2020**, *13*, 5203. [CrossRef]

- Ledin, J.A. Hardware-in-the-Loop Simulation. 1999. Available online: https://idsc.ethz.ch/content/dam/ethz/special-interest/ mavt/dynamic-systems-n-control/idsc-dam/Lectures/Embedded-Control-Systems/AdditionalMaterial/Applications/APP\_ Hardware-in-the-Loop\_Simulation.pdf (accessed on 24 June 2021).

- 11. Ren, W.; Steurer, M.; Baldwin, T.L. Improve the Stability and the Accuracy of Power Hardware-in-the-Loop Simulation by Selecting Appropriate Interface Algorithms. *IEEE Trans. Ind. Appl.* **2008**, *44*, 1286–1294. [CrossRef]

- 12. Jia, J.; Yang, G.; Nielsen, A.H.; Roenne-Hansen, P. Hardware-in-the-Loop Tests on Distance Protection Considering VSC Fault-Ride-through Control Strategies. *J. Eng.* 2018, 2018, 824–829. [CrossRef]

- 13. Vu, P.; Nguyen, Q.; Tran, M.; Todeschini, G.; Santoso, S. Adaptive Backstepping Approach for Dc-Side Controllers of Z-Source Inverters in Grid-Tied PV System Applications. *IET Power Electron.* **2018**, *11*, 2346–2354. [CrossRef]

- 14. Amin, M.; Aziz, G.A.A.; Durkin, J.; Mohammed, O.A. A Hardware-in-the-Loop Realization of Speed Sensorless Control of PMa-SynRM With Steady-State and Transient Performances Enhancement. *IEEE Trans. Ind. Appl.* **2019**, *55*, 5331–5342. [CrossRef]

- 15. Tian, J.; Liu, J.; Shu, J.; Tang, J.; Yang, J. Engineering Modelling of Wind Turbine Applied in Real-Time Simulation with Hardware-in-Loop and Optimising Control. *IET Power Electron.* **2018**, *11*, 2490–2498. [CrossRef]

- 16. Kotsampopoulos, P.C.; Kleftakis, V.A.; Hatziargyriou, N.D. Laboratory Education of Modern Power Systems Using PHIL Simulation. *IEEE Trans. Power Syst.* 2017, 32, 3992–4001. [CrossRef]

- 17. García-Martínez, E.; Sanz, J.F.; Muñoz-Cruzado, J.; Perié, J.M. A Review of PHIL Testing for Smart Grids—Selection Guide, Classification and Online Database Analysis. *Electronics* **2020**, *9*, 382. [CrossRef]

- El Mariachet, J.; Guan, Y.; Matas, J.; Martín, H.; Li, M.; Guerrero, J.M. HIL-Assessed Fast and Accurate Single-Phase Power Calculation Algorithm for Voltage Source Inverters Supplying to High Total Demand Distortion Nonlinear Loads. *Electronics* 2020, 9, 1643. [CrossRef]

- 19. Lucía, Ó.; Urriza, I.; Barragán, L.A.; Navarro, D.; Jiménez, Ó.; Burdío, J.M. Real-Time FPGA-Based Hardware-in-the-Loop Simulation Test Bench Applied to Multiple-Output Power Converters. *IEEE Trans. Ind. Appl.* **2011**, *47*, 853–860. [CrossRef]

- Sankaranarayanan, V.; Shirazi, M.; Gao, Y.; Ghosh, A.; Erickson, R.W.; Maksimovic, D. Controller Hardware-in-the-Loop Validation of a Modular Control Architecture for a Composite DC-DC Converter. In Proceedings of the 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, ON, Canada, 16–19 June 2019; pp. 1–7.

- Saralegui, R.; Sanchez, A.; Martínez-García, M.S.; Novo, J.; Castro, A. de Comparison of Numerical Methods for Hardware-In-the-Loop Simulation of Switched-Mode Power Supplies. In Proceedings of the 2018 IEEE 19th Workshop on Control and Modeling for Power Electronics (COMPEL), Padova, Italy, 25–28 June 2018; pp. 1–6.

- 22. Karaarslan, A. The Application of Hardware in the Loop for Single Phase Converters Based on DSP Controller at Solar Energy Systems. *Int. J. Electr. Energy* **2016**, *4*, 127–132. [CrossRef]

- Kiffe, A.; Schulte, T. FPGA-Based Hardware-in-the-Loop Simulation of a Rectifier with Power Factor Correction. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE'15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–8.

- 24. Woods, R.; McAllister, J.; Lightbody, G.; Yi, Y. *FPGA-Based Implementation of Signal Processing Systems*, 2nd ed.; John Wiley & Sons Inc.: Hoboken, NJ, USA, 2017; ISBN 978-1-119-07795-4.

- Faruque, M.D.O.; Strasser, T.; Lauss, G.; Jalili-Marandi, V.; Forsyth, P.; Dufour, C.; Dinavahi, V.; Monti, A.; Kotsampopoulos, P.; Martinez, J.A.; et al. Real-Time Simulation Technologies for Power Systems Design, Testing, and Analysis. *IEEE Power Energy Technol. Syst. J.* 2015, 2, 63–73. [CrossRef]

- 26. Jandaghi, B.; Dinavahi, V. Hardware-in-the-Loop Emulation of Linear Induction Motor Drive for MagLev Application. *IEEE Trans. Plasma Sci.* 2016, 44, 679–686. [CrossRef]

- Parma, G.G.; Dinavahi, V. Real-Time Digital Hardware Simulation of Power Electronics and Drives. *IEEE Trans. Power Deliv.* 2007, 22, 1235–1246. [CrossRef]

- Matar, M.; Iravani, R. FPGA Implementation of the Power Electronic Converter Model for Real-Time Simulation of Electromagnetic Transients. *IEEE Trans. Power Deliv.* 2010, 25, 852–860. [CrossRef]

- 29. Montano, F.; Ould-Bachir, T.; David, J.P. An Evaluation of a High-Level Synthesis Approach to the FPGA-Based Submicrosecond Real-Time Simulation of Power Converters. *IEEE Trans. Ind. Electron.* **2018**, *65*, 636–644. [CrossRef]

- Martínez-García, M.S.; de Castro, A.; Sanchez, A.; Garrido, J. Word Length Selection Method for HIL Power Converter Models. Int. J. Electr. Power Energy Syst. 2021, 129, 106721. [CrossRef]

- 31. Monti, A.; Stevic, M.; Vogel, S.; Doncker, R.W.D.; Bompard, E.; Estebsari, A.; Profumo, F.; Hovsapian, R.; Mohanpurkar, M.; Flicker, J.D.; et al. A Global Real-Time Superlab: Enabling High Penetration of Power Electronics in the Electric Grid. *IEEE Power Electron. Mag.* **2018**, *5*, 35–44. [CrossRef]

- 32. Nigam, S.; Ajala, O.; Dominguez-Garcia, A.D. A Controller Hardware-in-the-Loop Testbed: Verification and Validation of Microgrid Control Architectures. *IEEE Electrif. Mag.* 2020, *8*, 92–100. [CrossRef]

- Vijay, A.S.; Doolla, S.; Chandorkar, M.C. Real-Time Testing Approaches for Microgrids. *IEEE J. Emerg. Sel. Top. Power Electron.* 2017, 5, 1356–1376. [CrossRef]

- Sanchez, A.; de Castro, A.; Garrido, J. Parametrizable Fixed-Point Arithmetic for HIL With Small Simulation Steps. *IEEE J. Emerg.* Sel. Top. Power Electron. 2019, 7, 2467–2475. [CrossRef]

- 35. Ibarra, L.; Rosales, A.; Ponce, P.; Molina, A.; Ayyanar, R. Overview of Real-Time Simulation as a Supporting Effort to Smart-Grid Attainment. *Energies* **2017**, *10*, 817. [CrossRef]

- 36. Rodríguez-Andina, J.J.; Valdés-Peña, M.D.; Moure, M.J. Advanced Features and Industrial Applications of FPGAs—A Review. *IEEE Trans. Ind. Inform.* 2015, *11*, 853–864. [CrossRef]

- 37. SpHIL. Sp Control Technologies. Available online: http://spcontroltechnologies.com/sphil/ (accessed on 24 June 2021).

- Chakraborty, S.; Mazuela, M.; Tran, D.-D.; Corea-Araujo, J.A.; Lan, Y.; Loiti, A.A.; Garmier, P.; Aizpuru, I.; Hegazy, O. Scalable Modeling Approach and Robust Hardware-in-the-Loop Testing of an Optimized Interleaved Bidirectional HV DC/DC Converter for Electric Vehicle Drivetrains. *IEEE Access* 2020, *8*, 115515–115536. [CrossRef]

- Guillaud, X.; Faruque, M.O.; Teninge, A.; Hariri, A.H.; Vanfretti, L.; Paolone, M.; Dinavahi, V.; Mitra, P.; Lauss, G.; Dufour, C.; et al. Applications of Real-Time Simulation Technologies in Power and Energy Systems. *IEEE Power Energy Technol. Syst. J.* 2015, 2, 103–115. [CrossRef]

- 40. Parizad, A.; Mohamadian, S.; Iranian, M.E.; Guerrero, J.M. Power System Real-Time Emulation: A Practical Virtual Instrumentation to Complete Electric Power System Modeling. *IEEE Trans. Ind. Inform.* **2019**, *15*, 889–900. [CrossRef]

- 41. Jafarian, H.; Kim, N.; Parkhideh, B. Decentralized Control Strategy for AC-Stacked PV Inverter Architecture Under Grid Background Harmonics. *IEEE J. Emerg. Sel. Top. Power Electron.* **2018**, *6*, 84–93. [CrossRef]

- Srdic, S.; Liang, X.; Zhang, C.; Yu, W.; Lukic, S. A SiC-Based High-Performance Medium-Voltage Fast Charger for Plug-in Electric Vehicles. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6.

- 43. CRTS (HIL). Available online: https://powersmartcontrol.com/solutions/crts-hil/ (accessed on 2 May 2021).

- Delavari, A.; Brunelle, P.; Kamwa, I. Real-Time Closed-Loop PQ Control of NPC Multi-Level Converter Using OPAL-RT and Speedgoat Simulators. In Proceedings of the 2018 IEEE Electrical Power and Energy Conference (EPEC), Toronto, ON, Canada, 10–11 October 2018; pp. 1–5.

- Martínez, J.R.; Rengifo, H.R.; Córdoba, J.S.; Palacios, J.; Posada, J. Design and Implementation of a Multiplier SEPIC Converter to Emulate a Photovoltaic System Using Power HIL. In Proceedings of the 2019 FISE-IEEE/CIGRE Conference—Living the energy Transition (FISE/CIGRE), Medellin, Colombia, 4–6 December 2019; pp. 1–7.

- 46. Estrada, L.; Vázquez, N.; Vaquero, J.; de Castro, Á.; Arau, J. Real-Time Hardware in the Loop Simulation Methodology for Power Converters Using LabVIEW FPGA. *Energies* **2020**, *13*, 373. [CrossRef]

- 47. Zamiri, E.; Sanchez, A.; Yushkova, M.; Martínez-García, M.S.; de Castro, A. Comparison of Different Design Alternatives for Hardware-in-the-Loop of Power Converters. *Electronics* 2021, *10*, 926. [CrossRef]

- Carpiuc, S.; Schiesser, M.; Villegas, C. Current Control and FPGA–Based Real–Time Simulation of Grid–Tied Inverters. In Proceedings of the 2020 22nd European Conference on Power Electronics and Applications (EPE'20 ECCE Europe), Lyon, France, 7–10 September 2020; pp. P.1–P.7.

- 49. Amor Peinado, P. Estudio Avanzado de Herramientas Comerciales En HIL; Universidad Autónoma de Madrid: Madrid, Spain, 2020.

- Ayachit, A.; Kazimierczuk, M.K. Averaged Small-Signal Model of PWM DC-DC Converters in CCM Including Switching Power Loss. *IEEE Trans. Circuits Syst. II Express Briefs* 2019, 66, 262–266. [CrossRef]

- 51. Narimani, M.; Moschopoulos, G. Modeling and Control of a Single-Stage Three-Level Power Factor Correction AC-DC Converter. In Proceedings of the 2011 24th Canadian Conference on Electrical and Computer Engineering(CCECE), Niagara Falls, ON, Canada, 8–11 May 2011; pp. 000583–000586.

- 52. Bai, H.; Liu, C.; Breaz, E.; Al-Haddad, K.; Gao, F. A Review on the Device-Level Real-Time Simulation of Power Electronic Converters: Motivations for Improving Performance. *IEEE Ind. Electron. Mag.* **2021**, *15*, 12–27. [CrossRef]

- 53. Eickson, R.W.; Maksimovic, D. *Fundamentals of Power Electronics*, 2nd ed.; Springer: Norwell, MA, USA, 2001; ISBN 978-0-7923-7270-7.

- 54. Ji, F.; Fan, H.; Sun, Y. Modelling a FPGA-Based LLC Converter for Real-Time Hardware-in-the-Loop (HIL) Simulation. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 1016–1019.

- 55. Sira-Ramirez, H.; deNieto, M.D. A Lagrangian Approach to Average Modeling of Pulsewidth-Modulation Controlled DC-to-DC Power Converters. *IEEE Trans. Circuits Syst. I Fundam. Theory Appl.* **1996**, *43*, 427. [CrossRef]

- Rosa, A.H.R.; Morais, L.M.F.; Seleme, I.S. Hardware in the Loop Simulation of Non Linear Control Methods Applied for Power Converters. In Proceedings of the 2015 IEEE 13th Brazilian Power Electronics Conference and 1st Southern Power Electronics Conference (COBEP/SPEC), Fortaleza, Brazil, 29 November–2 December 2015; pp. 1–6.

- 57. NAVARRO, D.; CORTES, D.; GALAZ-LARIOS, M. A Port-Hamiltonian Approach to Control DC-DC Power Converters. *Stud. Inform. Control.* **2017**, 26. [CrossRef]

- Rosa, A.H.R.; Morais, L.M.F.; Seleme, I.S. A Study and Comparison of Nonlinear Control Techniques Apply to Second Order Power Converters Using HIL Simulation. In Proceedings of the 2016 12th IEEE International Conference on Industry Applications (INDUSCON), Curitiba, Brazil, 20–23 November 2016; pp. 1–8.

- Dufour, C.; Cense, S.; Bélanger, J. FPGA-Based Switched Reluctance Motor Drive and DC-DC Converter Models for High-Bandwidth HIL Real-Time Simulator. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–8.

- 60. Lamo, P.; de Castro, Á.; Brañas, C.; Azcondo, F.J. Emulator of a Boost Converter for Educational Purposes. *Electronics* **2020**, *9*, 1883. [CrossRef]

- Paquin, J.; Belanger, J.; Snider, L.A.; Pirolli, C. Wei Li Monte-Carlo Study on a Large-Scale Power System Model in Real-Time Using EMEGAsim. In Proceedings of the 2009 IEEE Energy Conversion Congress and Exposition, San Jose, CA, USA, 20–24 September 2009; pp. 3194–3202.

- 62. Lu, B.; Wu, X.; Figueroa, H.; Monti, A. A Low-Cost Real-Time Hardware-in-the-Loop Testing Approach of Power Electronics Controls. *IEEE Trans. Ind. Electron.* 2007, 54, 919–931. [CrossRef]

- 63. Karimi, S.; Poure, P.; Saadate, S. An HIL-Based Reconfigurable Platform for Design, Implementation, and Verification of Electrical System Digital Controllers. *IEEE Trans. Ind. Electron.* **2010**, *57*, 1226–1236. [CrossRef]

- 64. Adzic, E.; Grabic, S.; Vekic, M.; Porobic, V.; Celanovic, N.F. Hardware-in-the-Loop Optimization of the 3-Phase Grid Connected Converter Controller. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 5392–5397.

- Chai, E.; Celanovic, I.; Poon, J. Validation of Frequency- and Time-Domain Fidelity of an Ultra-Low Latency Hardware-in-the-Loop (HIL) Emulator. In Proceedings of the 2013 IEEE 14th Workshop on Control and Modeling for Power Electronics (COMPEL), Salt Lake City, UT, USA, 23–26 June 2013; pp. 1–5.

- Grégoire, L.; Al-Haddad, K.; Nanjundaiah, G. Hardware-in-the-Loop (HIL) to Reduce the Development Cost of Power Electronic Converters. In Proceedings of the India International Conference on Power Electronics 2010 (IICPE2010), New Delhi, India, 28–30 January 2011; pp. 1–6.

- Lamo, P.; Ruiz, G.A.; Pigazo, A.; Azcondo, F.J. Low THDi Controller for Current Sensorless Single Phase Rectifiers Using a Two-Sample Phase Locked Loop. In Proceedings of the 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, CO, Canada, 17–20 June 2019; pp. 1–5.

- 68. Lopez, V.M.; Azcondo, F.J.; de Castro, A.; Zane, R. Universal Digital Controller for Boost CCM Power Factor Correction Stages Based on Current Rebuilding Concept. *Power Electron. IEEE Trans.* **2014**, *29*, 3818–3829. [CrossRef]

- 69. Sanchez, A.; de Castro, A.; López, V.M.; Azcondo, F.J.; Garrido, J. Single ADC Digital PFC Controller Using Precalculated Duty Cycles. *IEEE Trans. Power Electron.* **2014**, *29*, 996–1005. [CrossRef]

- López, F.; López-Martín, V.M.; Azcondo, F.J.; Corradini, L.; Pigazo, A. Current-Sensorless Power Factor Correction With Predictive Controllers. *IEEE J. Emerg. Sel. Top. Power Electron.* 2019, 7, 891–900. [CrossRef]

- 71. Rosa, A.H.R.; De Souza, T.M.; Morais, L.M.F.; Seleme, S.I. Adaptive and Nonlinear Control Techniques Applied to SEPIC Converter in DC-DC, PFC, CCM and DCM Modes Using HIL Simulation. *Energies* **2018**, *11*, 602. [CrossRef]

- 72. Rosa, A.H.R.; Morais, L.M.F.; Fortes, G.O.; Seleme Júnior, S.I. Practical Considerations of Nonlinear Control Techniques Applied to Static Power Converters: A Survey and Comparative Study. *Int. J. Electr. Power Energy Syst.* 2021, 127, 106545. [CrossRef]

- 73. Bouafassa, A.; Fernández-Ramírez, L.M.; Babes, B. Power Quality Improvements of Arc Welding Power Supplies by Modified Bridgeless SEPIC PFC Converter. *J. Power Electron.* **2020**, 20, 1445–1455. [CrossRef]

- 74. Amiri, P.; Gautam, D.; Botting, C.; Eberle, W.; Wang, L. Real-Time Hardware-in-the-Loop Simulation and Control of Totem Pole PFC Converter. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; pp. 1–7.

- Monmasson, E.; Cirstea, M.N. FPGA Design Methodology for Industrial Control Systems—A Review. *IEEE Trans. Ind. Electron.* 2007, 54, 1824–1842. [CrossRef]

- 76. Corradini, L. Analysis and Implementation of Digital Control Architectures for DC-DC Switching Converters. Ph.D. Thesis, University of Padua, Padova, Italy, January 2008.

- 77. Peterchev, A.V.; Sanders, S.R. Quantization Resolution and Limit Cycling in Digitally Controlled PWM Converters. *IEEE Trans. Power Electron.* **2003**, *18*, 301–308. [CrossRef]

- Kang, R.; Kim, S.; Yang, I.; Jeong, K.; Kang, C.; Kim, G. The Use of FPGA in HIL Simulation of Three Phase Interleaved DC-DC Converter. In Proceedings of the 2012 IEEE Vehicle Power and Propulsion Conference, Seoul, Korea, 9–12 October 2012; pp. 772–776.

- Van de Sype, D.M.; De Gusseme, K.; Van den Bossche, A.P.; Melkebeek, J.A. Small-Signal Laplace-Domain Analysis of Uniformly-Sampled Pulse-Width Modulators. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), Aachen, Germany, 20–25 June 2004; Volume 6, pp. 4292–4298.

- 80. HIL602 | Typhoon HIL.HIL. Available online: https://www.typhoon-hil.com/ (accessed on 24 June 2021).